天眼查显示,北京北方华创微电子装备有限公司近日取得一项名为“一种集成电路的制造工艺”的专利,授权公告号为CN113506731B,授权公告日为2024年7月23日,申请日为2016年10月8日。

背景技术

在集成电路制造工艺领域,目前通常使用硅基材料制造集成电路,硅 (或者多晶硅)在空气中放置的情况下表面会自然氧化形成一层致密的二氧化硅(SiO2)层。在有些工艺中,例如,在金属硅化物(Silicide) 工艺中,金属镍铂(NiPt)薄膜要与硅衬底直接接触,如果衬底表面有一层 SiO2,则会增加电阻率,影响器件性能,因此,制造后续工艺前需要去除这层SiO2。而在去除这层SiO2的同时,必须保护其他薄膜/结构不能被去除或者损伤,隔离层(Spacer,由氮化硅(Si3N4)材料制成)的线宽尺寸会影响器件电性,如漏电(leakage)增加等。因此,需要在去除 SiO2的同时尽量保持隔离层(Spacer,Si3N4)不被去除。

现有工艺多采用湿法刻蚀、等离子体干法刻蚀等方法去除SiO2,其对Si3N4的刻蚀选择比低,对隔离层去除过多,造成隔离层尺寸缩小,增大漏电,从而影响器件性能。

因此,有必要开发一种应用于集成电路制造工艺中的高选择比、高效率的去除晶片上的二氧化硅的方法。

公开于本发明背景技术部分的信息仅仅旨在加深对本发明的一般背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

发明内容

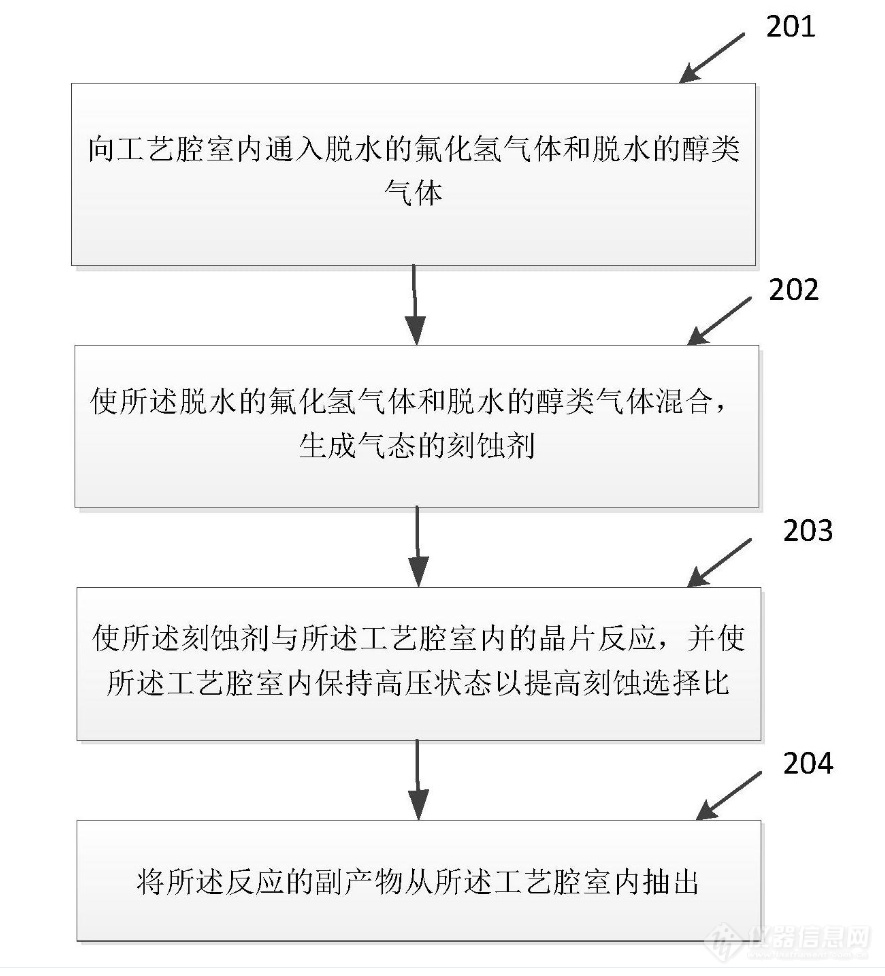

公开了一种集成电路的制造工艺,包括:去除晶片上的二氧化硅的方法,该方法可包括:向工艺腔室内通入脱水的氟化氢气体和脱水的醇类气体;使所述脱水的氟化氢气体和脱水的醇类气体混合,生成气态的刻蚀剂;使所述刻蚀剂与所述工艺腔室内的晶片反应,并使所述工艺腔室内保持高压状态以提高刻蚀选择比;以及将所述反应的副产物从所述工艺腔室内抽出。根据本发明的集成电路的制造工艺中,去除晶片上的二氧化硅的方法通过使气态的刻蚀剂在高压力下与二氧化硅直接反应,并在反应后将反应产物抽出,实现高选择比、高效率地去除二氧化硅。

[来源:仪器信息网] 未经授权不得转载

2024.08.16

设备担重任,创芯闯征程-第十二届半导体设备与核心部件展示会9月底将于无锡开幕

2024.08.19

粤芯半导体“一种半导体器件中的互连金属的沉积方法”专利获授权

2024.08.16

中国大陆全球领先!2023年全球集成电路产业综合竞争力百强城市出炉

2024.08.15

提交30亩生产基地申请,晶工半导体将进一步提升晶圆倒角机产能

2024.08.14

2024.08.14

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~