随着人工智能应用的快速发展,AI算力系统对于高效能互连技术的需求呈现爆发性增长态势。为了满足这一挑战,业界正大力研发更大容量、更高速率、更高集成度的硅基光互连芯片解决方案,把硅光收发芯片直接集成到计算芯片附近或同一封装内,将极大地减少信号传输的延迟和功耗,从而显著提升算力系统的整体性能。然而,面向下一代单通道200G以上(200G per lane)的光接口速率需求,硅光方案在速率、功耗、集成度等方面面临着巨大挑战。

近日,国家信息光电子创新中心(NOEIC)和鹏城实验室的光电融合联合团队完成了2Tb/s硅光互连芯粒(chiplet)的研制和功能验证,在国内首次验证了3D硅基光电芯粒架构,实现了单片最高达8×256Gb/s的单向互连带宽。

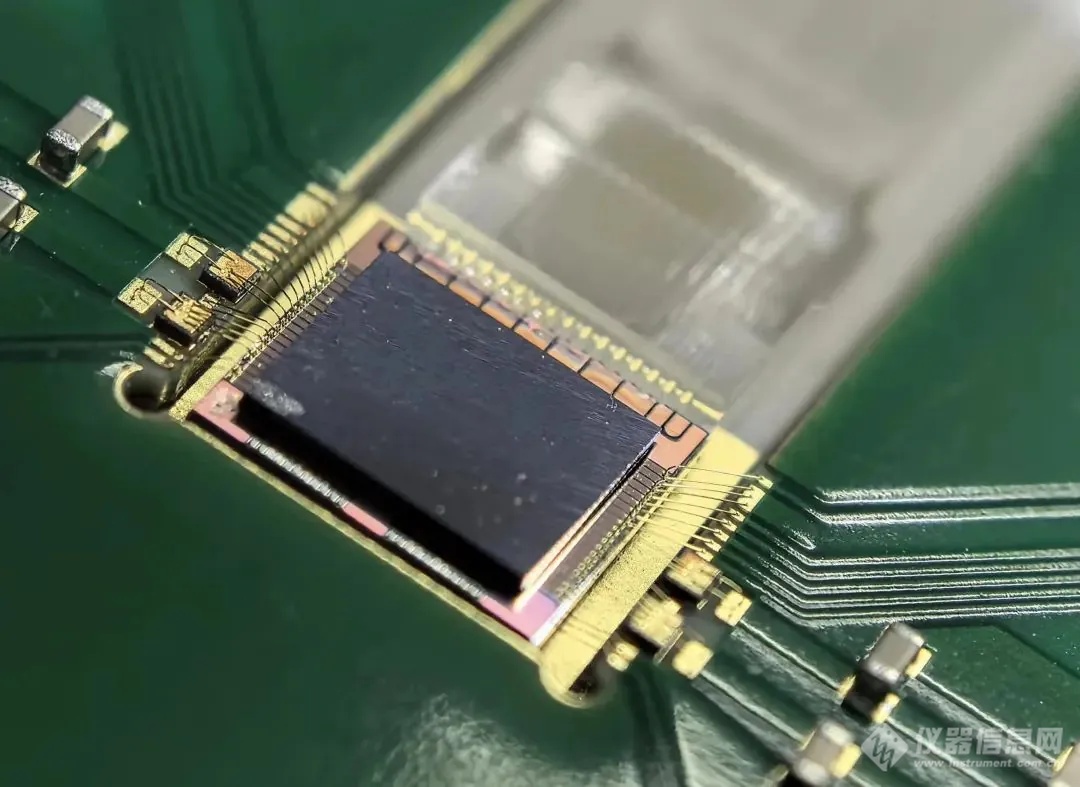

团队在2021年1.6T硅光互连芯片的基础上,进一步突破了光电协同设计仿真方法,研制出硅光配套的单路超200G driver和TIA芯片, 并攻克了硅基光电三维堆叠封装工艺技术,形成了一整套基于硅光芯片的3D芯粒集成方案。

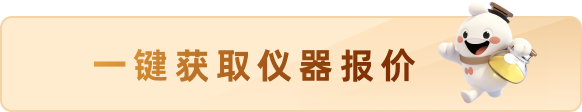

2Tb/s 硅基3D集成光发射芯粒

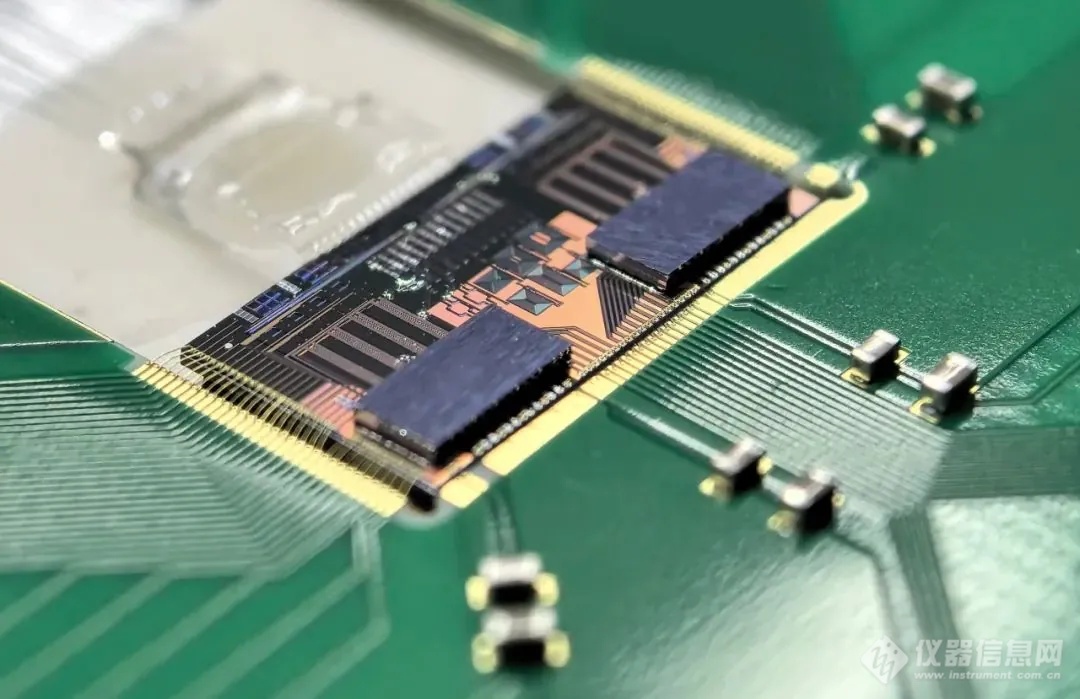

2Tb/s 硅基3D集成光接收芯粒

硅光互连芯粒的侧向显微镜结构

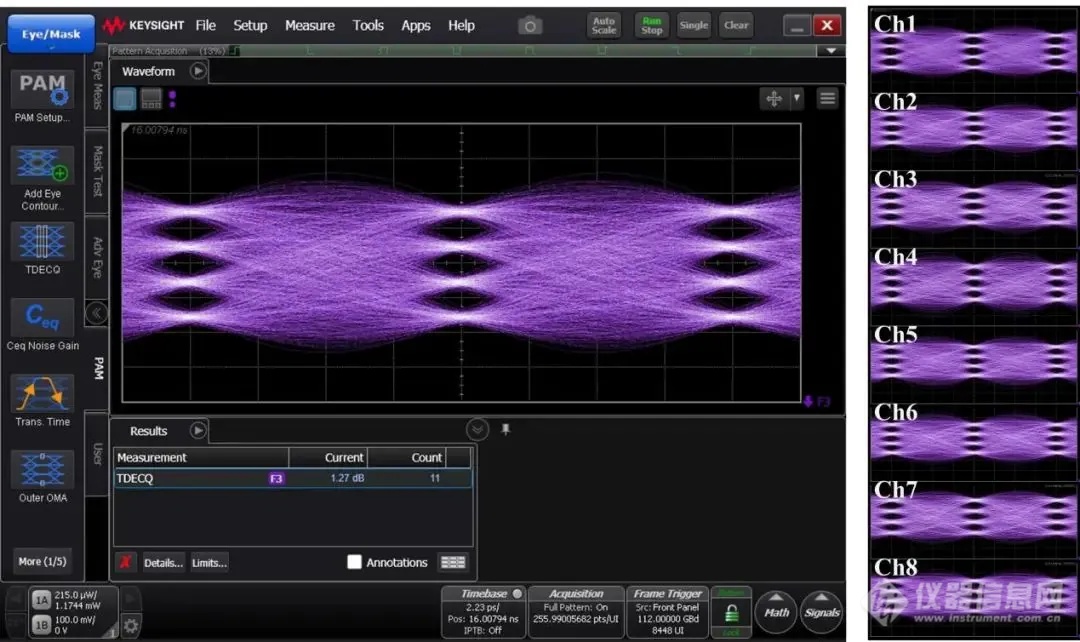

该方案充分利用了硅光与CMOS封装工艺兼容的特点,相比于传统wirebond方案,3D芯粒能解决电芯片与光芯片间高密度、高带宽电互连的困难,显著降低射频信号在光-电芯片互连过程中的严重衰减。经系统传输测试,8个通道在下一代光模块标准的224Gb/s PAM4光信号速率下,TDECQ均在2dB以内。通过进一步链路均衡,最高可支持速率达8×256Gb/s,单片单向互连带宽高达2Tb/s。

8×224Gb/s硅基光发射芯粒输出眼图

该工作充分展现了3D集成硅光芯粒的优越互连性能,以及联合团队的领先自主研发水平。成果将广泛应用于下一代算力系统和数据中心所需的CPO、NPO、LPO、LRO等各类光模块产品中,为国内信息光电子技术的率先突围探索出可行路径。

[来源:国家信息光电子创新中心]

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~