天眼查显示,北京华大九天科技股份有限公司近日取得一项名为“一种集成电路版图满足相邻通孔最小间距约束的布线方法”的专利,授权公告号为CN115358181B,授权公告日为2024年8月6日,申请日为2022年8月5日。

背景技术

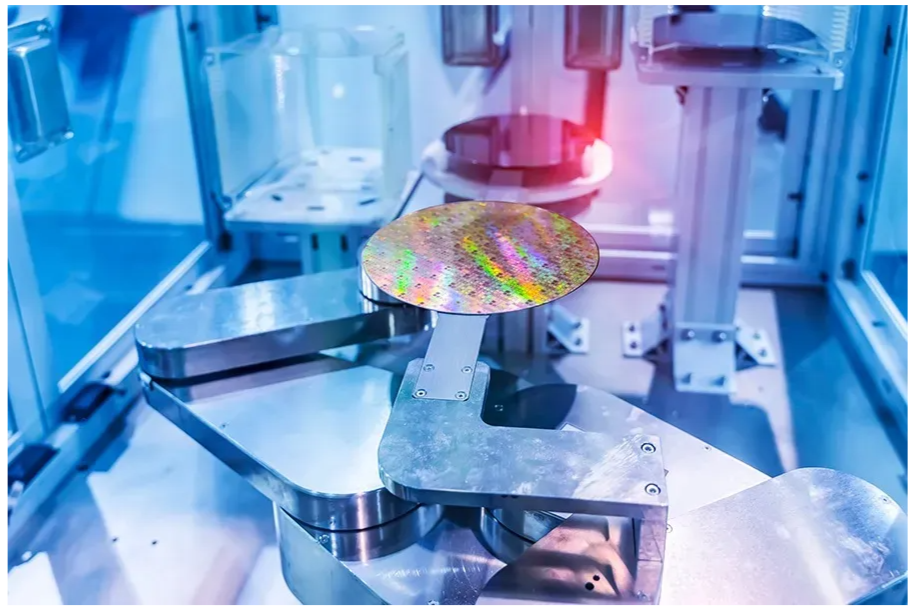

随着芯片设计规模的不断增大以及制造工艺的不断提升,EDA工具成了芯片设计领域必不可少的辅助工具。在布线阶段,EDA工具的首要目标是实现不同模块之间的连接关系。EDA工具在实现连接关系的同时还需要满足设计规则,这是因为设计规则与制造工艺息息相关,会直接影响最后芯片的制造。

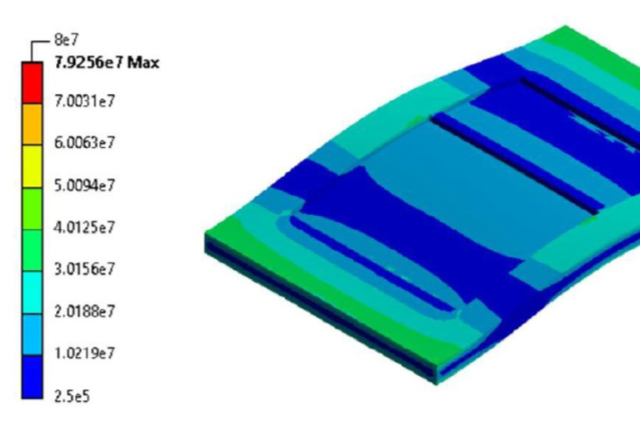

芯片设计规则包含了众多约束,相邻通孔最小间距(MinAdjacentViaSpacing)约束就是其中之一。MinAdjacentViaSpacing约束是对相邻的通孔之间间距的要求。应用该约束需要满足一定条件,即,通孔之间距离小于或等于相邻通孔距离称为相邻通孔,当前通孔的相邻通孔的数量大于或等于设计规则规定的相邻通孔数量时,该约束发挥作用。

以往采用的方法是在当前创建的通孔的所涉及的顶层、cut层、底层、三层版图中所有的版图图形进行遍历,如果遍历到的图形为通孔则与当前通孔进行检查,判断是否满足MinAdjacentViaSpacing约束。但是随着设计规模和复杂性的递增,该方法消耗的时间会大幅增加,面临巨大的时间成本。

发明内容

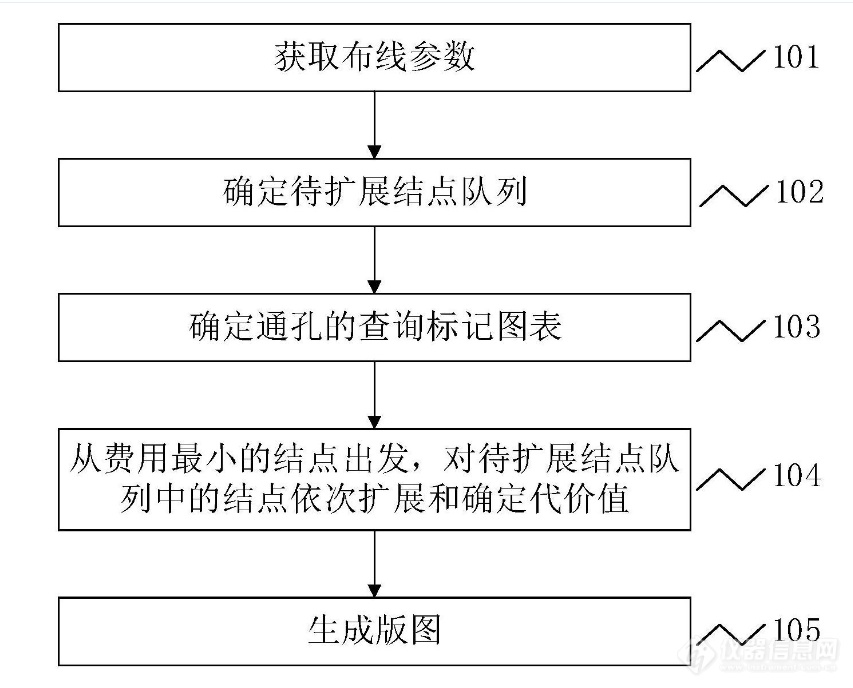

本发明提供了一种集成电路版图满足相邻通孔最小间距约束的布线方法,包括以下步骤:1)获取布线参数,确定布线约束;2)将需要连接的源点加入到待扩展结点的队列中,确定待扩展结点队列;3)遍历版图图形,确定通孔的第一查询标记图表和第二查询标记图表;4)从费用最小的结点出发,对待扩展结点队列中的结点通过查询第一查询标记图表和第二查询标记图表依次进行扩展和确定代价值;5)生成版图。本发明可以减少布线所需要消耗的时间,提高布线效率。

[来源:仪器信息网] 未经授权不得转载

2024.08.16

汇顶科技“打码控制及打码方法、系统、芯片、电子设备及存储介质”专利获授权

2024.08.16

2024.08.16

飞恩微“芯片粘接质量检验方法、装置、设备及存储介质”专利获授权

2024.08.16

2024年Q2全球芯片市场规模攀升至1500亿美元,中国同比增长21.6%

2024.08.15

2024.08.12

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~