此前有消息称,台积电2nm制程工艺将于本周试产,苹果将独占首批产能,用于制造iPhone 17用芯片。不仅如此,消息称台积电下一代3D封装先进平台SoIC(系统整合芯片)也规划用于苹果M5芯片,预计将在2025年量产,SoIC月产能将从当前的4000片至少扩大一倍,2026年有望实现数倍增长。海外机构预测,苹果M5芯片有望大幅提升计算性能,可用于人工智能(AI)服务器。

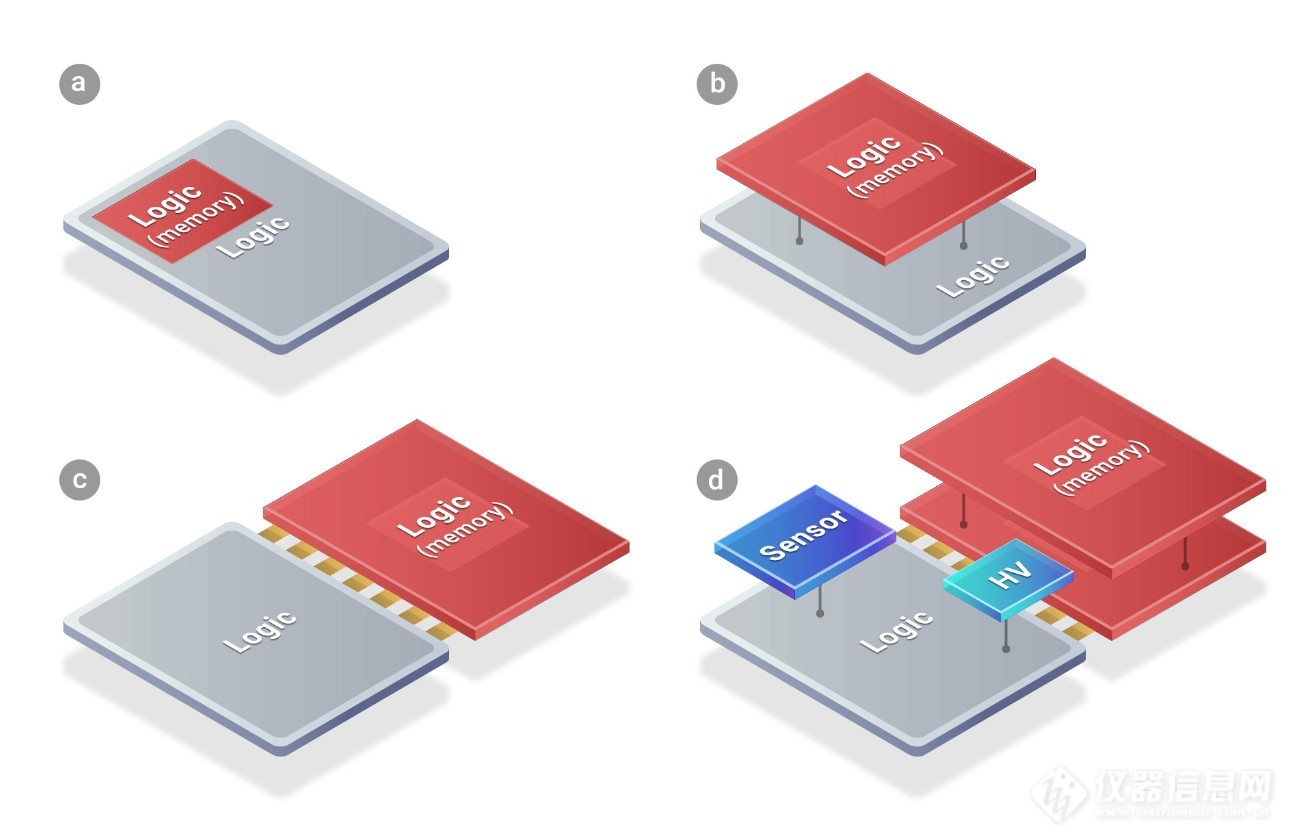

随着SoC(系统级芯片)越来越大,未来12英寸晶圆恐怕只能制造一颗芯片,但这对晶圆代工厂的良率及产能是重大挑战。以台积电为首的生态,试图通过SoIC立体堆叠封装技术,来避免单颗芯片面积持续扩大带来的弊端,且能够满足SoC芯片对于晶体管数量、接口数、传输质量及运行速度的要求。

台积电示意图:a为传统SoC,b、c、d为SoIC不同方案

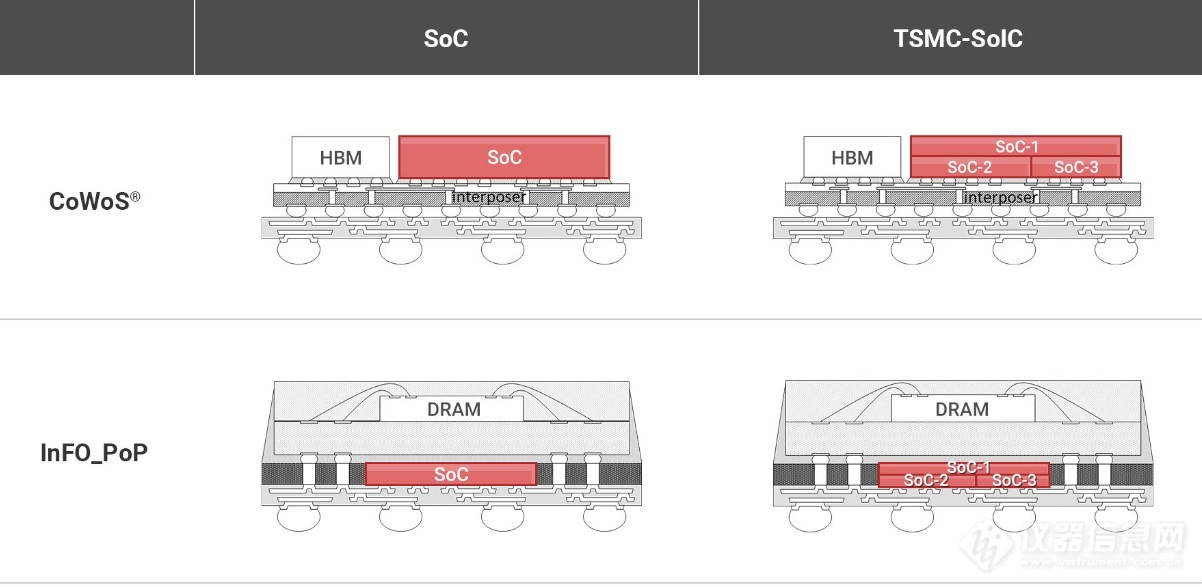

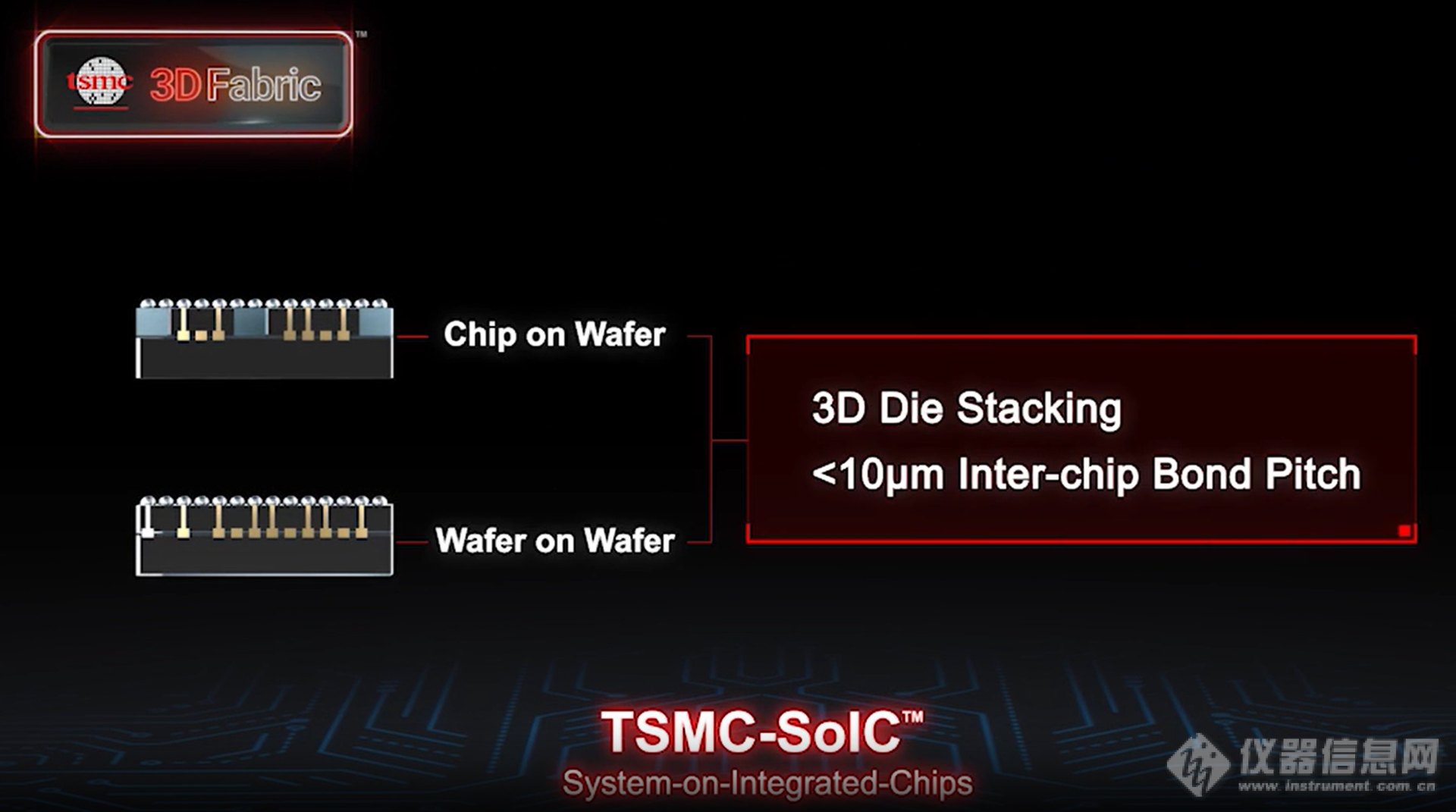

台积电3D封装中的TSMC-SoIC技术包含多种形态(Chip on Wafer、Wafer on Wafer),可将多颗同构或异构小芯片垂直、水平紧密堆叠,集成为一颗类似单颗SoC的芯片。随后,这种SoIC可进一步通过CoWoS、InFO_PoP等封装技术,与HBM等DRAM芯片进行组合。

业界指出,SoIC的关键——混合键合技术(Hybrid Bonding)是未来AI/HPC芯片互联的主流革命性技术,英伟达与AMD目前都在寻求SoIC混合键合间距降至6μm~4.5μm,目前台积电的技术能力为10μm及以下。

中国台湾业界表示,AMD MI300系列芯片为率先导入SoIC封装的产品,虽仍处于良率爬坡阶段,但其余大厂皆十分感兴趣。观察今年台积电各大客户动态,除争取3nm抢下更多产能外,也参考CoWoS发展经验,对SoIC封装技术展现高度兴趣。

[来源:爱集微]

2024.07.13

台积电订单大增25%!英伟达追加Blackwell架构GPU订单

2024.07.16

2024.07.08

2024.07.05

2024.07.05

2024.07.05

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~