半导体&电子测试测量,投稿:kangpc@instrument.com.cn

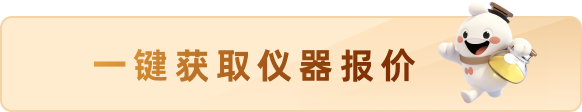

半导体设备巨头东京电子近日宣布,其位于东京电子宫城的开发团队(其等离子体蚀刻系统的开发和制造基地)开发了一种创新的蚀刻技术,能够在堆叠超过400层的先进3D NAND器件中生产存储沟道孔。该团队开发的新工艺首次将介电蚀刻应用于低温范围,生产出具有极高蚀刻率的系统。这项创新技术不仅可以在33分钟内实现高深宽比的10µm深蚀刻,而且与以前的技术相比,还可以将全球变暖的可能性降低84%。蚀刻结构的几何形状非常明确,如图1所示。这项技术带来的潜在创新将推动更大容量的3D NAND闪存的开发。

图1.蚀刻后的存储器沟道孔图案的截面SEM图像和孔底部的FIB切割图像。

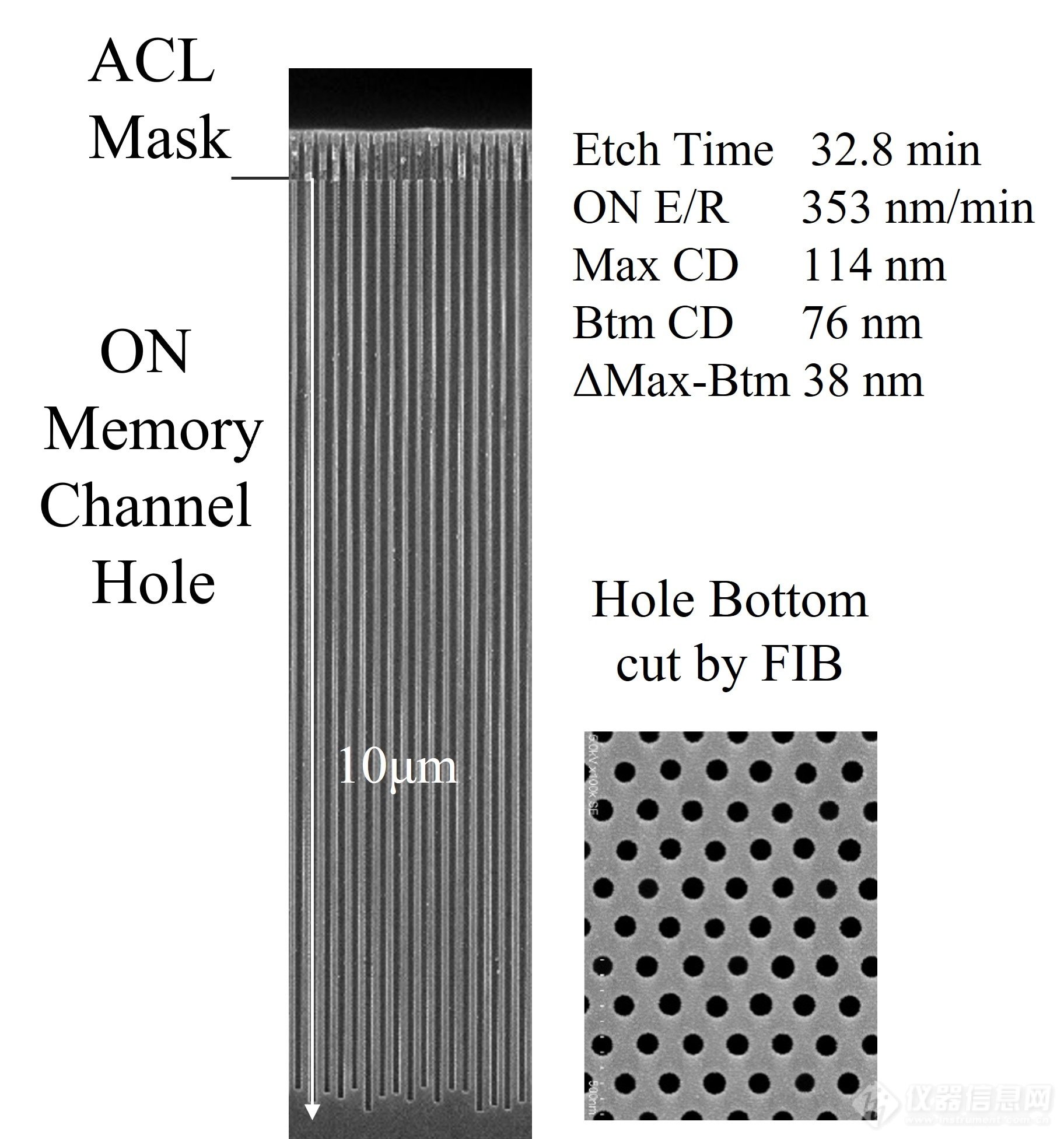

图2 3D NAND闪存

TEL开发这项技术的团队在6月11日至6月16日在京都举行的2023年超大规模集成电路技术与电路研讨会上提交其研究结果报告,该研讨会是最负盛名的半导体研究国际会议之一。

[来源:仪器信息网译] 未经授权不得转载

2021.06.11

2024.07.19

中微公司:未来5-10年目标覆盖50%-60%集成电路关键设备

2024.05.31

等离子体刻蚀机、PVD和扫描电镜等创新成果亮相2024清华大学工程博士论坛!

2024.05.20

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~