半导体&电子测试测量,投稿:kangpc@instrument.com.cn

当地时间6月16日,应用材料公司宣布推出了一种全新的先进逻辑芯片布线工艺技术,可微缩到3纳米及以下技术节点。

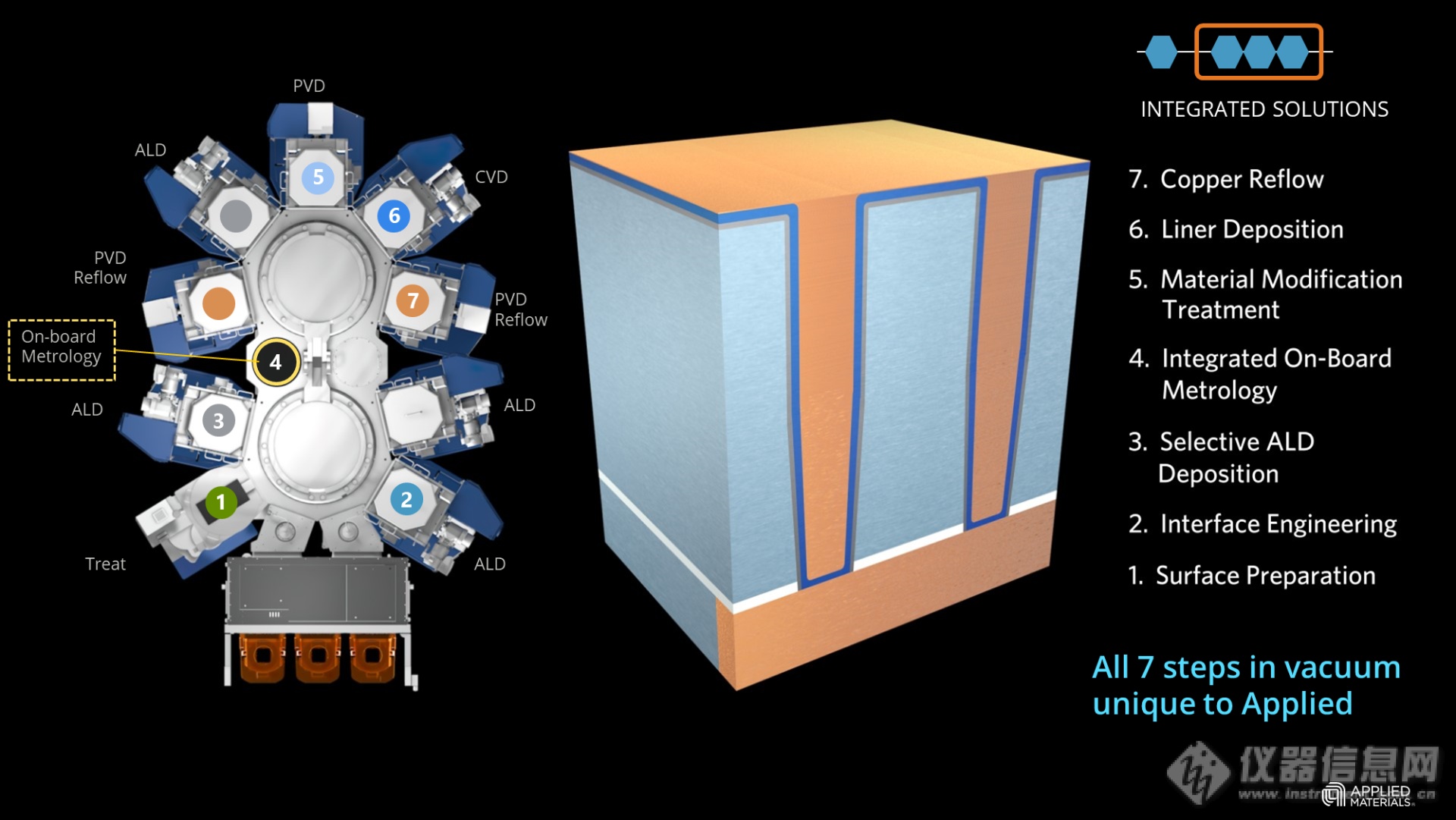

虽然尺寸微缩有利于提高晶体管性能,但互连布线的情况则恰好相反:较小的电线却具有更大的电阻,从而降低了性能并增加了功耗。如果没有材料工程的突破,通过互连从7nm节点到3nm节点电阻将增加10倍,从而抵消晶体管缩放的优势。

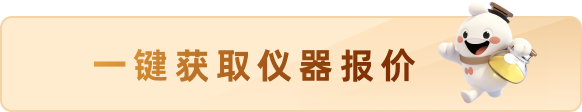

应用材料公司开发了一种名为Endura® Copper Barrier Seed IMS™的全新的解决方案。它是一种集成材料解决方案,在高真空下将七种不同的工艺技术组合在一个系统中:ALD、PVD、CVD、铜回流、表面处理、接口工程和计量。该组合将符合要求的 ALD 替换为选择性 ALD,从而消除了通过接口的高电阻性障碍。该解决方案还包括铜回流技术,使空隙自由缺口填补了狭窄的功能。通过接触接口的电阻降低高达 50%,提高芯片性能和功耗,使逻辑扩展继续扩展到 3nm 及以上。

应用材料半导体产品集团高级副总裁兼总经理普拉布·拉贾(Prabu Raja)表示:"智能手机芯片拥有数百亿的铜互连,线路已经消耗了芯片三分之一的电量。"在真空中集成多种工艺技术使我们能够重新设计材料和结构,使消费者能够拥有更强大的设备和更长的电池寿命。这种独特的集成解决方案旨在帮助客户改善性能、功率和面积成本。”

Endura® Copper Barrier Seed IMS™系统现在正被全球领先的逻辑节点代工厂客户使用。

[来源:仪器信息网译] 未经授权不得转载

2021.05.08

2024.07.22

2024.07.19

新品上市|FLIR X系列科研级热像仪,确保测试不丢帧、无数据损失!

2024.06.27

2024.05.09

2024.04.03

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~