显微镜行业的老兵/游历近50国仍永不停歇的旅行者/NAUI认证的高级潜水员。

上篇聊的偏粗线条,这篇会聊一些更细节的半导体“黑话”,还有就是这些半导体独立王国的“语言”和我们“正常人”说的话到底有什么关联,毕竟半导体行业不是凭空出世的,芯片人更不是“空降兵”,这个细分领域的技术和应用是有其根基和土壤的;

“正常”电镜人里做冷场发射电镜CFESEM的,特别是做氦离子显微镜HIM的,都熟悉“Anneal”这个术语,指的是通过瞬间加热灯尖驱逐吸附的气体分子,增强钨单晶的活性以便于灯尖切削,俗称“重生”;半导体对“Anneal”的”黑话“称呼差别比较大叫回火,又称退火,也是对wafer进行热处理的一种手段;更广义地讲,集成电路IC工艺中所有的在氮气等不活泼气氛中进行的热处理的过程,都可以称为退火;”退火“与“重生”异曲同工,目的一是激活杂质,使不在晶格位置上的离子运动到晶格位置,以便具有电活性,产生自由载流子,起到掺入杂质Doping的作用;二是消除损伤,离子植入Ion Implatation后回火是为了修复因高能加速的离子直接打入芯片而产生的损毁区;由于进入底材Substrate中的离子行进中将硅原子撞离原来的晶格位置,而导致的晶体的特性改变就叫损毁;而这种损毁区,经过回火的热处理后即可复原。这种热处理的回火功能可利用其温度、时间差异来控制全部或局部的活化植入离子的功能。氧化制程中也有回火工序,主要是为了降低SiO2的晶格结构。退火方式有传统的炉Furnace退火,还有更先进的快速退火:包括脉冲激光法、连续波激光、非相干宽带频光源;如卤光灯、电弧灯、石墨加热器、红外设备等;“Furnace”在透射电镜TEM样品加热杆Heating holder上很常见,就是“坩埚”。

这里提到的离子植入Ion Implantation对熟悉FIB的“正常人“并不陌生,传统聚焦离子束利用Ga+离子束进行切割Milling、截面Sectioning、或是在气体注入系统GIS的配合下做刻蚀Etching,离子束在不同的气体配合下,可以做到选择性刻蚀Selective Etching,或增强型刻蚀Enhanced Etching;在FIB中,掺杂物Dopant对样品的掺杂Doping,我们是不希望看到的,注入到样品里的Ga+会被视为对样品的污染Contamination;而晶圆制造中的离子植入,是在原本本征的半导体里主动的植入或通过扩散的方法将其它的原子或离子掺杂进去,达到改变其电性能的方法,这里,我们是希望看到样品wafer性能发生改变的;

甚至,当一般植入的离子分布达不到要求时,还会加码,通过进炉管Furnace加高温的方式将离子进行扩散Diffusion,以达到我们对离子分布的要求,同时对离子植入造成的缺陷进行修复;这里涉及到的设备叫扩散炉Diffusion furnace;此工序就是在扩散炉管内通以饱和的杂质蒸汽,使芯片表面有一高浓度的杂质层,然后以高温使杂质驱入扩散,快速完成固态扩散需要约数亿年才能完成的任务;Diffusion虽然能较精确地选择杂质Dopant的数量,但受限于离子能量,无法将杂质驱入芯片更深(um级别)的区域了;因此需借着原子有从高浓度往低浓度扩散的性质,在相当高的温度去进行,一方面将杂质扩散到较深的区域,且使杂质原子占据硅原子位置,产生所要的电性,另外也可将植入时产生的缺陷消除;此方法就称为驱入Drive-In;“Drive-in“在这里就不是那种能直接开车进去看电影的露天电影院了;”Drive-In”工艺中,不再加入半导体杂质总量,只将表面的杂质往半导体内更深入的推进;在驱入时,常通入一些氧气﹒因为硅氧化时,会产生一些缺陷,如空洞Vacancy;这些缺陷会有助于杂质原子的扩散速度;电镜中用到的超高真空泵-离子泵Ion Getter Pump,有和上面说的半导体的“Drive-in”手段类似,通过将杂质气体分子驱入离子泵的钛合金板,逐步达到提升真空的功效;顺便一句,半导体制程中用到的”特种气体“,”黑话“叫”特气“。

还记得”正常“电镜上熟悉的用来做表层污染物去除的Plasma cleaner等离子清洗吗?电子枪和电子光学镜筒装配前会用来轰击清洁样品表面,避免超高真空下的发气outgassing,俗称”轰击台“;晶圆制程中的这类设备就叫Arc Chamber弧光反应室,和“轰击台”原理一样,事实上设备就是利用一个直流式的电浆发生器,操作电流产生的弧光电浆来清洁抛光晶圆表面;这里的电浆就是又一句半导体“黑话”,正常人一般叫它Plasma,或等离子体;电浆Plasma是人类近代物化史上重大的发现之一,指的是一个遭受部分离子化的气体,气体里面的组成有各种带电荷的电子,离子,及不带电的分子和原子团等;电浆发生器的两金属极板上加上直流电压而产生的电浆我们就叫它直流电浆DC Plasma了;

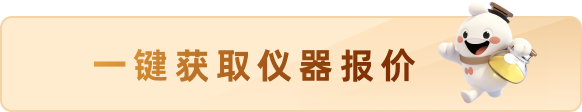

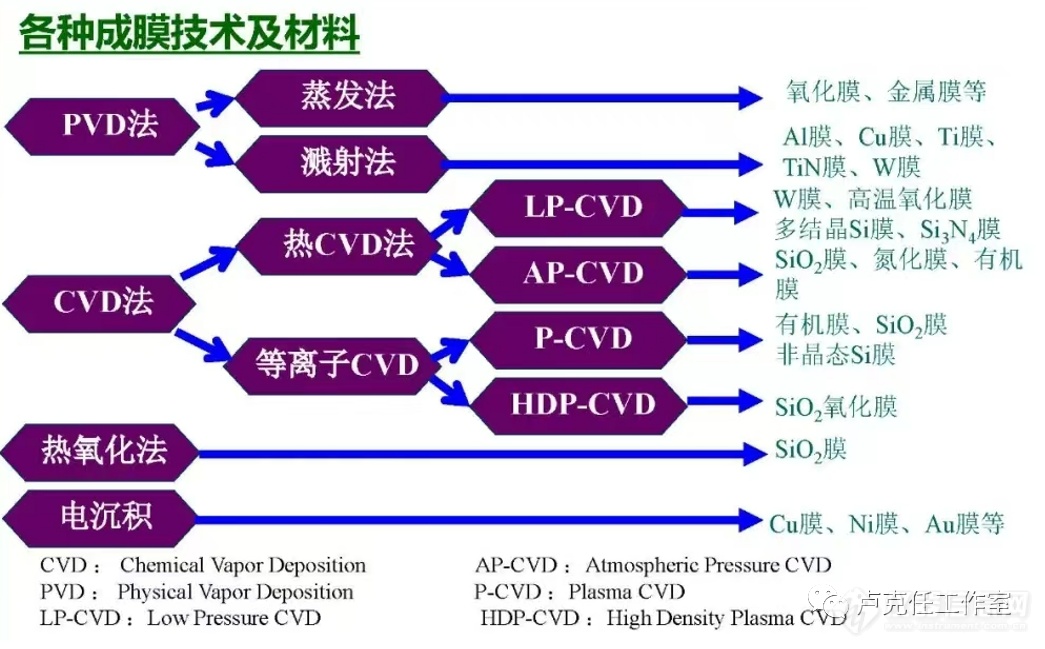

提到电浆,就顺便说下晶圆的镀膜Deposition环节;相比较使用化学蒸气沉积CVD Chemical Vapor Deposition方法的镀膜,使用物理蒸气沉积法PVD的镀膜工艺在高制程中更常被用到;PVD制程中,脱离电浆的带正电荷离子,在暗区的电场的加速下,获得高能量,当离子与阴电极产生轰击之后,基于能量传递的原理,离子轰击除了会产生二次电子以外,还会把电极表面的原子给"打击"出来,称为sputtering溅射;电极板加直流电压称为DC Sputtering直流溅射;阴极导电材料,因为像“靶子“被电浆打击,被称为靶材Target;说到这里,我嘘了一口气;终于,半导体人也不是必须只讲自己人的”黑话“,他们跟”正常人“一样,还是能讲些”人话“的;

需要溅射镀膜比较细腻的可以用磁控DC溅镀机:为了使离子在往金属靶表面移动时获得足够的能量,除了提高极板间的电压外,还必须使离子在阴极暗区内所遭受的碰撞次数降低,就必须降低溅渡的压力,越低越好,以增长离子的平均自由行程;这样一来,单位体积内的气体分子数降低,使得电浆里的离子浓度也降低,导致溅渡薄膜的沉积速率变慢,整体镀膜更加细腻;“正常”电镜实验室中,为了增加样品导电性,我们会去给样品镀一层金膜,这里的“镀金仪”就是缩小版的Fab里的PVD设备了;除了“镀金”,我们还经常会去“镀碳”;碳膜比起金膜来,可以增强样品表层导电性,但不会影响到“打能谱”,标定样品的化学元素信息;所以生物样品常用镀金,材料样品更愿意镀碳,就是这个道理;

我们利用Sputtering溅射技术镀金,镀碳的技术则为Evaporation蒸镀;Fab里的采用蒸镀技术的PVD设备,就是将蒸镀源放在坩埚Furnace里加热,当温度升高到接近蒸镀源的熔点附近时,原本处于固态的蒸镀源的蒸发能力将会特别强,利用这些被蒸发出来的原子,就可在附着在离其不远处的芯片Wafer表面上,形成薄膜式的沉积层,这种方法就是蒸镀Evaporation了;

随着用以隔离之用的场氧化层FOX,CMOS电晶体,金属层及介电层等构成IC的各个结构在Chip芯片上建立之后,芯片的表面也将随之变得上下凸凹不平,致使后续制程变得更加困难;所以,传统半导体制程就开始执行芯片表面平坦化的技术了;以介电层SiO2的平坦化为例,有高温热流法、各种回蚀技术及旋涂式玻璃法;当 超大规模集成电路 VeryLarge Scale Integration- VLSI的制程推进到0.35um以下后,上面这些技术就不能满足制程需求了,故而也就产生了Chemically Mechanical Polishing化学机械研磨法CMP制程;所谓CMP就是利用在表面布满研磨颗粒的研磨垫Polishing pad,对凸凹不平的晶体表面,藉由化学助剂Reagent的辅助,以化学反应和机械式研磨等双重的加工动作,来进行其表面平坦化的处理;看到这里,您不难看出,这个半导体的CMP不就是我们“正常”实验室人经常操作的电化学抛光Electro-ChemicalPolishing制样流程吗?怎么什么进了半导体应用的门槛就非得改名,开说“黑话“呢?

由于半导体芯片行业薪酬普遍高出“正常“行业一头,导致在这个行业里的从业人沾沾自喜;笔者接触过一位有幸掌握了CMP操作技术的年轻人,”下界“来做电镜售后,满脑子都是半导体厂里的条条框框,动辄fingerpointing这个那个流程不够详细规范,无法操作,责任不明等等,俨然就是一位被半导体惯坏Spoiled的巨婴,”下凡“之后连正常思考都不会了;这里例子让我知道了即使在光鲜的半导体行业里,也会培养出只知规程,而实际却”四体不勤,五谷不分“的庸才。

通篇看到这里,要是您要还没说“服了You”的话,那下面我们再接着多看多学一堆半导体的”黑话“吧;

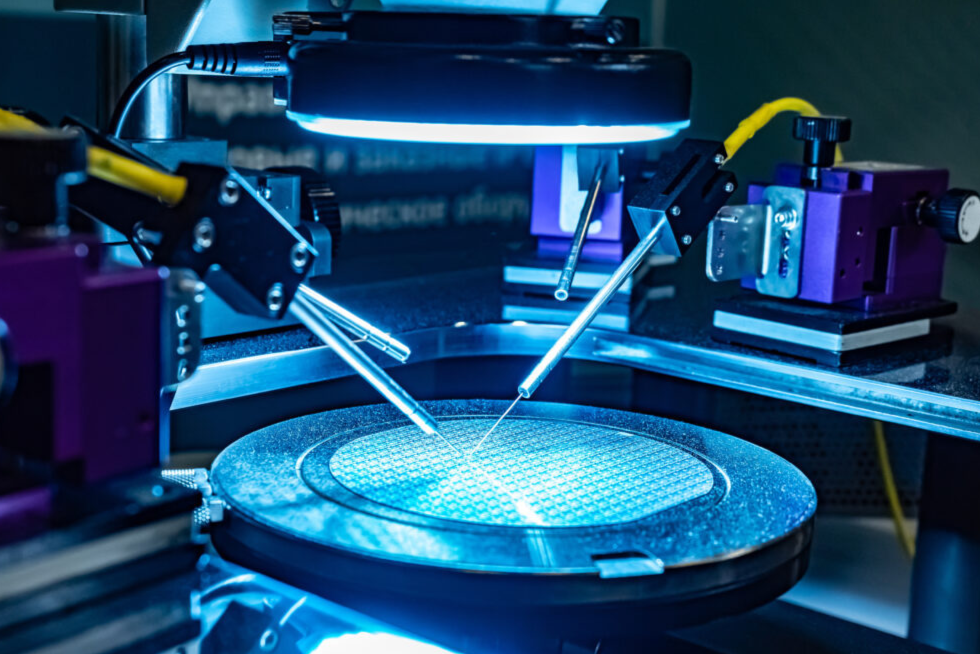

一片大硅片、OR晶圆,即Wafer上有许多相同的方形小单位,这些小单位叫Die,大家在这里肯定都理解这不是那个常用动词了吧?不过学材料的同学,你们知道它“黑话“叫“晶粒“吗?这回不淡定了吧;同一片上的每个Die晶粒都是相同的构造,具有相同的功能,每个晶粒经切割封装后,就制成了一颗颗我们日常生活中常用的IC芯片了,所以每一个大晶圆片所能造出的小IC数量是很可观的;同样地,如果因制造的疏忽而产生的缺陷,往住波及到同一批次Lot里成百成千个产品;说到这里,各位看官也明白为什么晶圆厂都喜欢300mm,就是12英寸的大硅片了吧;没错,一次出货出的多,省耗材省时间,人人喜大普奔;这里再来个插科打诨,Die的复数这里“黑话“叫Dice;没错,就是我们耍的”骰子“一个词;让我们期盼这来之不易的晶圆片不会轻易地godie,好不容易划片成功的裸Die不会变态地被当骰子耍吧;

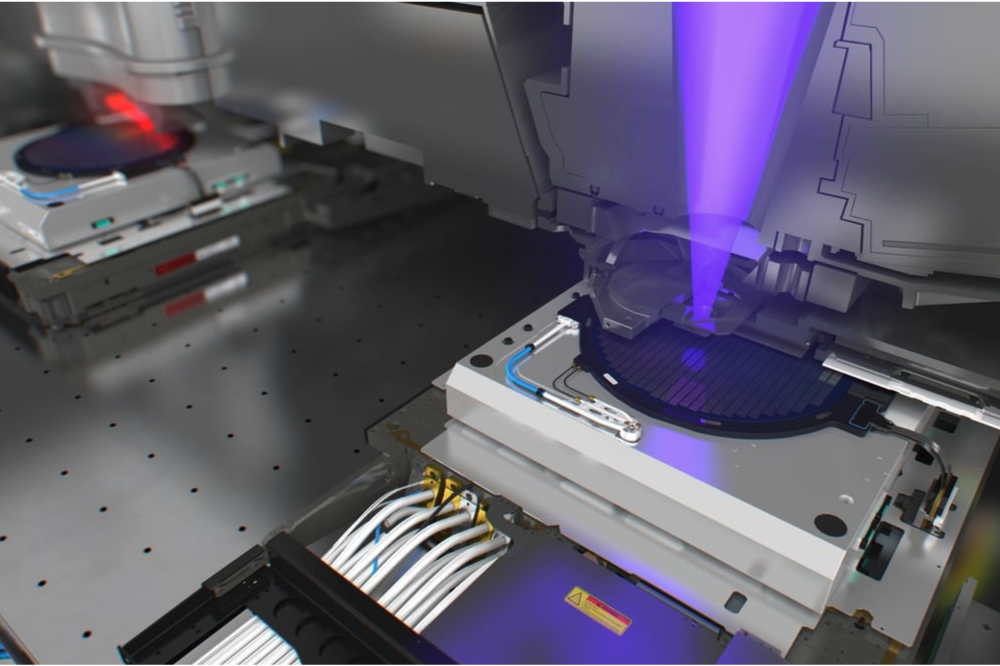

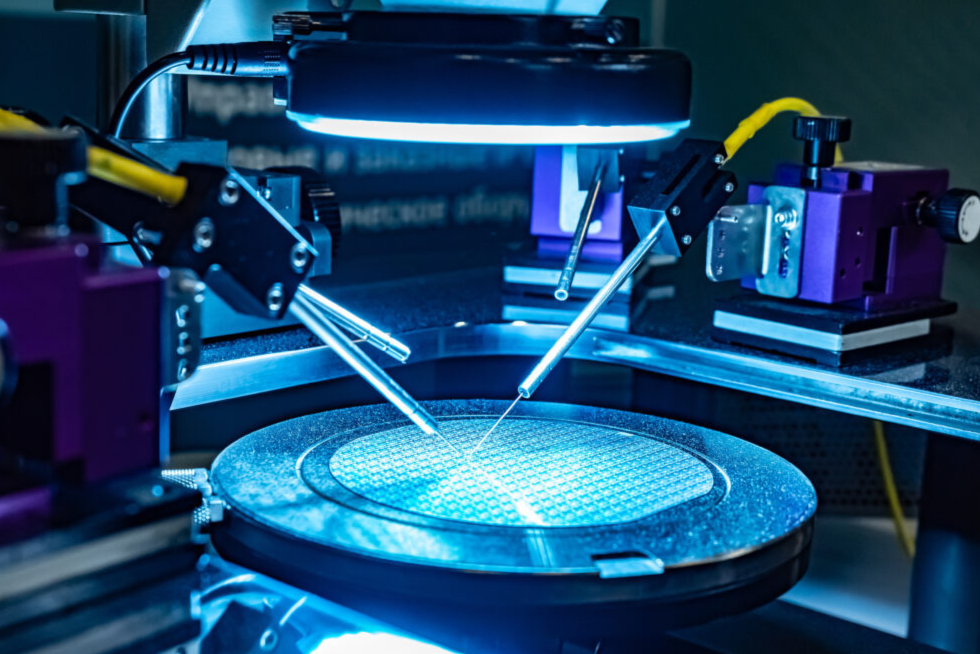

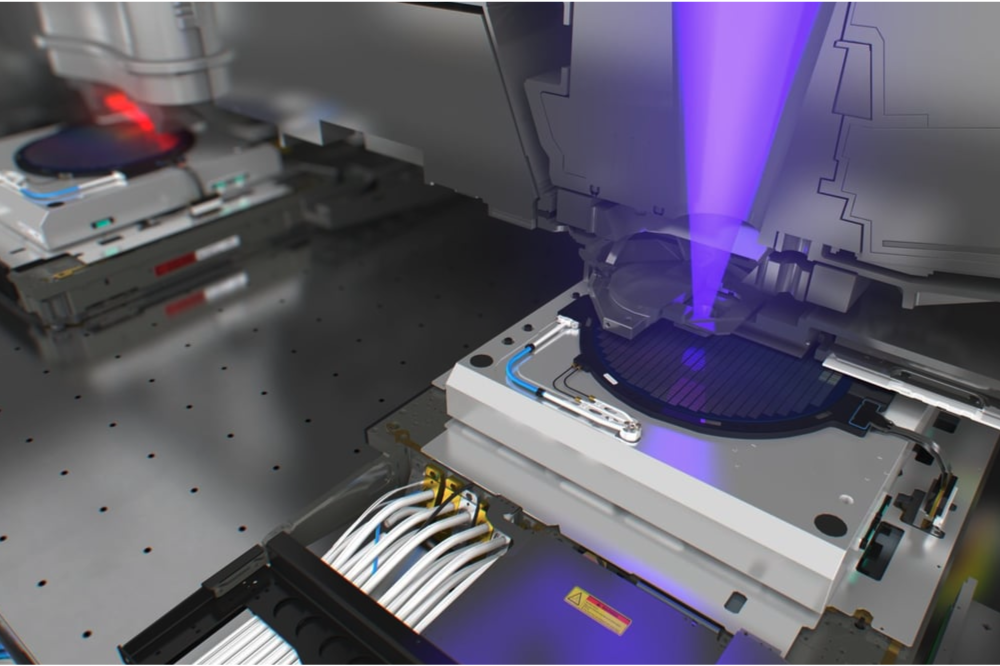

Fab里最贵的三类设备,也就是晶圆制造前道工艺中的三大设备了;除了上面提到的各类“D”类Deposition沉积镀膜设备,其余两大设备就是听得耳朵都长茧子的的光刻机Photolithography“L“类设备,和光刻后的刻蚀机Etching”E“类设备了;

目前海外Fab使用最广泛的光刻机就是DUV深紫外光刻Deep-UV lithography,和ASML动辄卖上亿美元一台的EUV极紫外光刻机Extreme-UV lithography了;不知不觉中,ASML和EUV似乎成了光刻机的代名词;事实上,能够在硅基上“刻”出图案的技术有多种:X射线光刻 X-ray lithography、电子束光刻 Electron beamlithography EBL、氦离子束光刻 Helium ion beam lithography、等离子体飞秒激光光刻Femtosecond Plasma Lithography FPL、纳米压痕刻Nano Imprint Lithography NIL;这么多种类的光刻技术,光刻机的供应商自然不会只有ASML一家,ASML倒确实是唯一一家既可以做EUV光刻,也能做EBL光刻的光刻机“大户”;ASML是在收购了用13260只电子束EBL跟它PK光刻老大败北的Mapper后,同时获得这项技术的;

上面有提到可以说是半导体芯片行业使用频率可以排名前三的“黑话”,叫Fabless,业务里不做Fab的就叫Fabless;我们现在聊到了光刻,曝光时需要拿一片事先印好图形玻璃模板叫Mask或Reticle,放在光源与物镜之间的这一类叫做光罩Mask光刻,DUV、EUV光刻就是这类了;同理,曝光过程中不用模板辅助显影,而是光源直接接触硅片的技术就叫无光罩Maskless光刻了,带电粒子束光刻,也就是电子束、离子束一类光刻就属于这类了;“黑话”的特性是除了“道上”的同行,别人都听不懂的;这里的Maskless就又是一个“活生生”半导体的“黑话“的例子;

既然提到“曝光“exposure,我们就顺便聊下半导体”盗用“摄影师的这条行话吧;早期照相机底片的感光原理在集成电路的制造过程中也适用;借助”曝光“,可以将光罩,又叫光掩模,也就是Mask上的事先定义的图形Pattern,转移到晶圆片上,借助大数值孔径Numerical Aperture NA的物镜的帮助,形成了更为精细的光阻图形;所以如果”光刻“是晶圆制造中最关键的一步的话,”曝光“便是”光刻“中那个最重要的步骤;既然重要,这里我们就多聊两句”黑话“:以使用最广的5XStepper为例,其方式就是把对紫外线UV敏感的光阻膜PR当作照相机的底片,光罩上是芯片架构师用EDA设计的各种图形,以特殊波长的光线,比如G-Line 436nm照射穿过光罩,经过物镜,又叫缩小镜或Reduction Lens后,光罩上的图形则呈5倍缩小,精确地定义在”底片“,也就是芯片上的光阻膜,又叫光刻胶或Photoresist,再经过显影Development后,即可将照到光线的正光阻膜显掉,从而就得到了我们心心念念地想要的各种精细图形,准备好为下一步的刻蚀或离子植入制程使用;因为光阻膜对于某特定波长的光线特别敏感,所以Fab厂都有黄光区,将一切照明用光源统一过滤成昏黄色,以避免泛白光源中含有对光阻有感光能力的波长成份存在,否则会发生光线污染,扰乱精细的光阻成形。

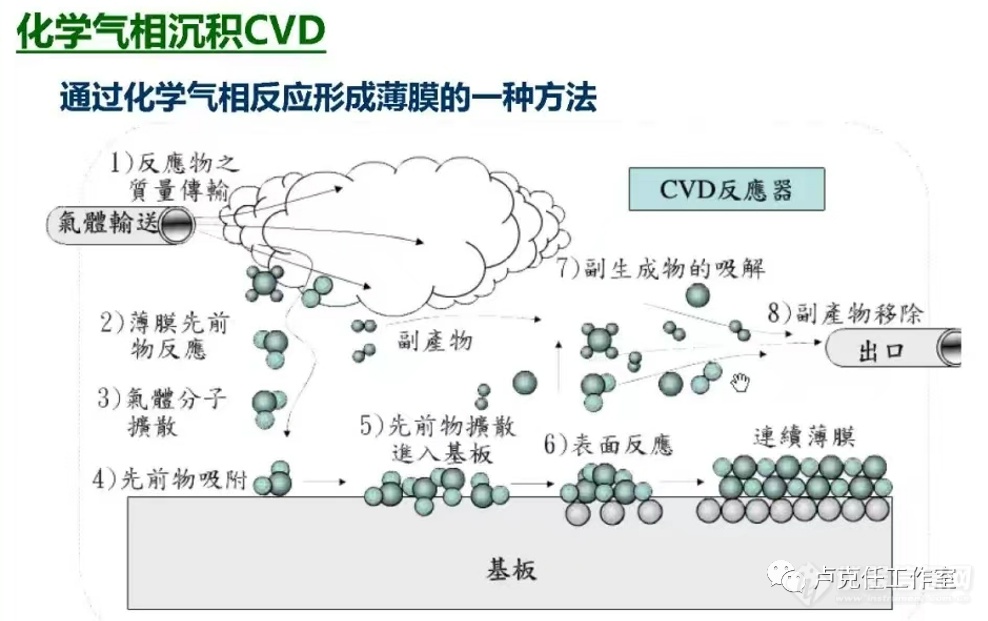

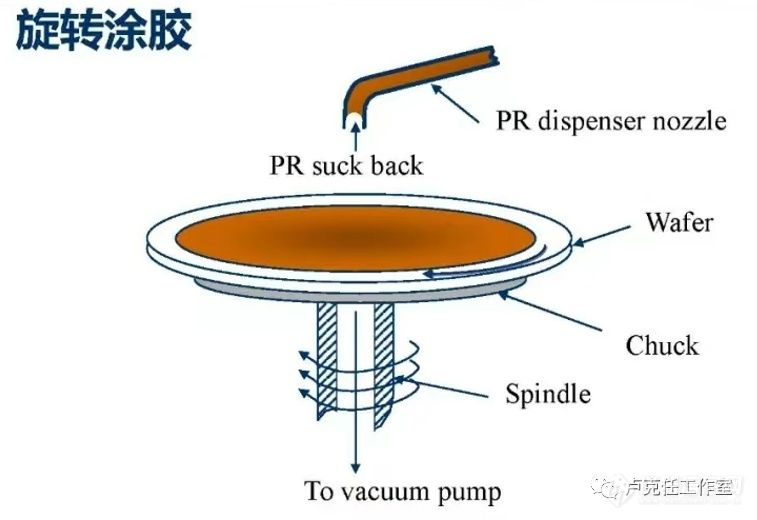

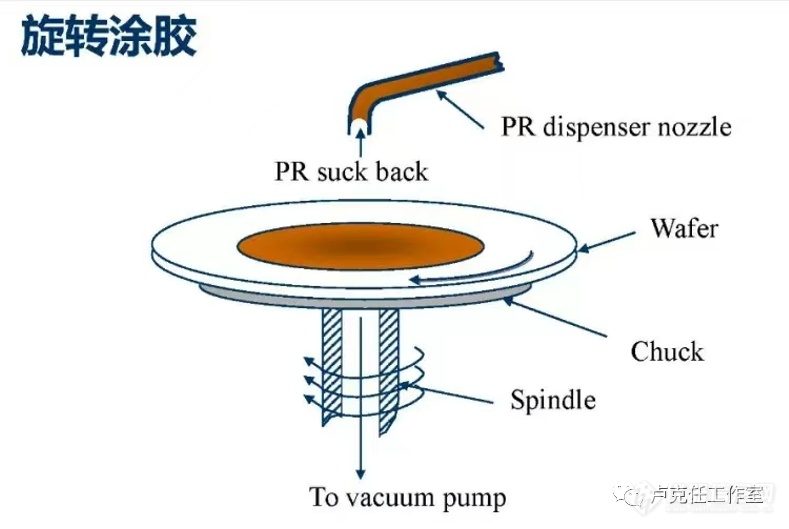

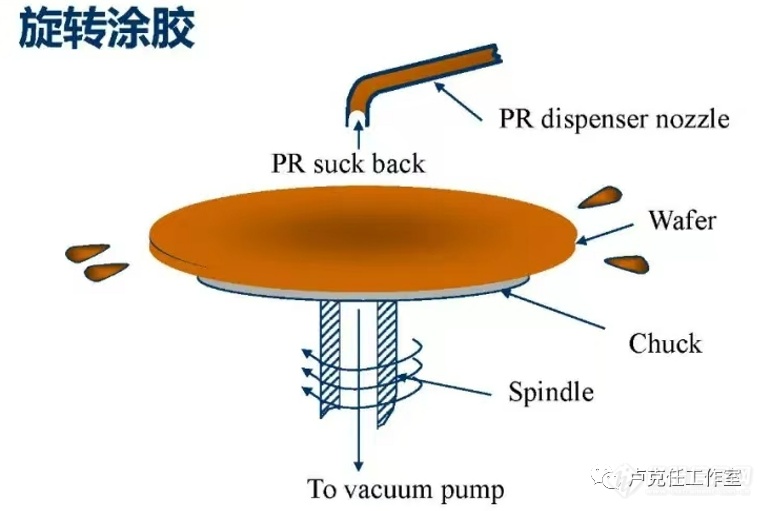

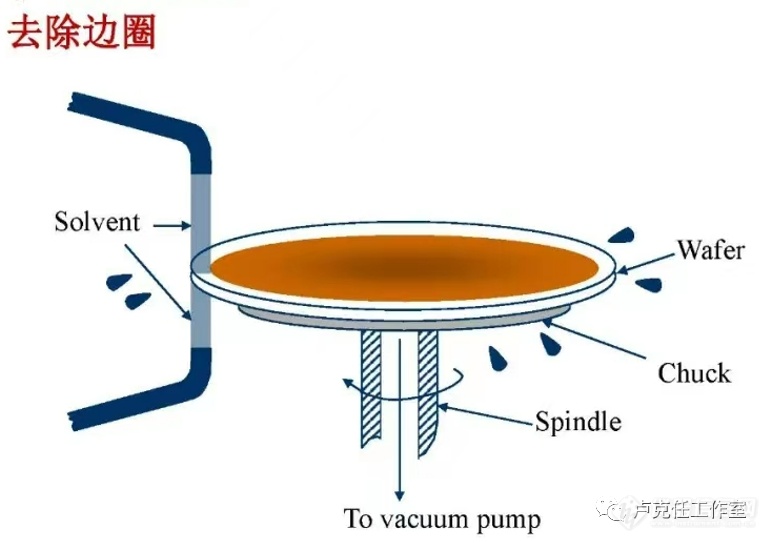

就像胶片时代的照相底片一样,光刻胶 photoresist,又称光阻剂,也有正负之分;半导体的负片叫负性光刻胶negative photoresist,正片叫正性光刻胶 positive photoresist,较高制程的Fab多会用到正胶,显影时正胶会被显没,留下底下需要被刻蚀掉的硅片区域;“光刻胶“叫起来比”光阻剂“更加顺口,也算是一句标准的下凡“黑话”吧;这个关于光刻胶的“黑话”群还包括:无机光刻胶 inorganic resist、多层光刻胶 multilevel resist、电子束光刻胶 electron beam resist、X射线光刻胶 X-ray resist等分类;还有甩胶 spinning、涂胶 coating、烘胶 baking、去胶stripping、氧化去胶 removing by oxidation、等离子体去胶 removing of by plasma,等等。

曝光工艺里还时不时地会听到还分接触式曝光法contact exposure、接近式曝光法 proximity exposure、还有投影式曝光法 projection exposure的说法,这是不是让刚刚觉得自己懂了点晶圆制造的半导体小白,只瞅了一眼半导体的世界,一下子又跌回了“深渊“呢?

半导体“黑话“这次就先聊止于此,下篇是Save the best to the last,最精彩的那一集大结局;敬请期待。

[来源:仪器信息网] 未经授权不得转载

2022.12.26

ASML或将Hyper-NA EUV光刻机定价翻倍,让台积电、三星和英特尔犹豫不决

2024.07.03

2024.07.03

2024.07.03

2024.06.27

2024.06.20

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~