经过数十年发展,半导体工艺制程已逐渐逼近亚纳米物理极限,传统硅基集成电路难以依靠进一步缩小晶体管面内尺寸来延续摩尔定律。发展垂直架构的多层互连CMOS逻辑电路以实现三维集成技术的突破,已成为国际半导体领域积极探寻的新方向。在2023年12月美国旧金山召开的国际电子器件会议(IEDM)中,三星、台积电等半导体公司争相发布相关研究计划。

由于硅基晶体管的现代工艺采用单晶硅表面离子注入的方式,难以实现在一层离子注入的单晶硅上方再次生长或转移单晶硅。虽然可以通过三维空间连接电极、芯粒等方式提高集成度,但是关键的晶体管始终被限制在集成电路最底层,无法获得厚度方向的自由度。新材料或颠覆性原理因此成为备受关注的重要突破点。

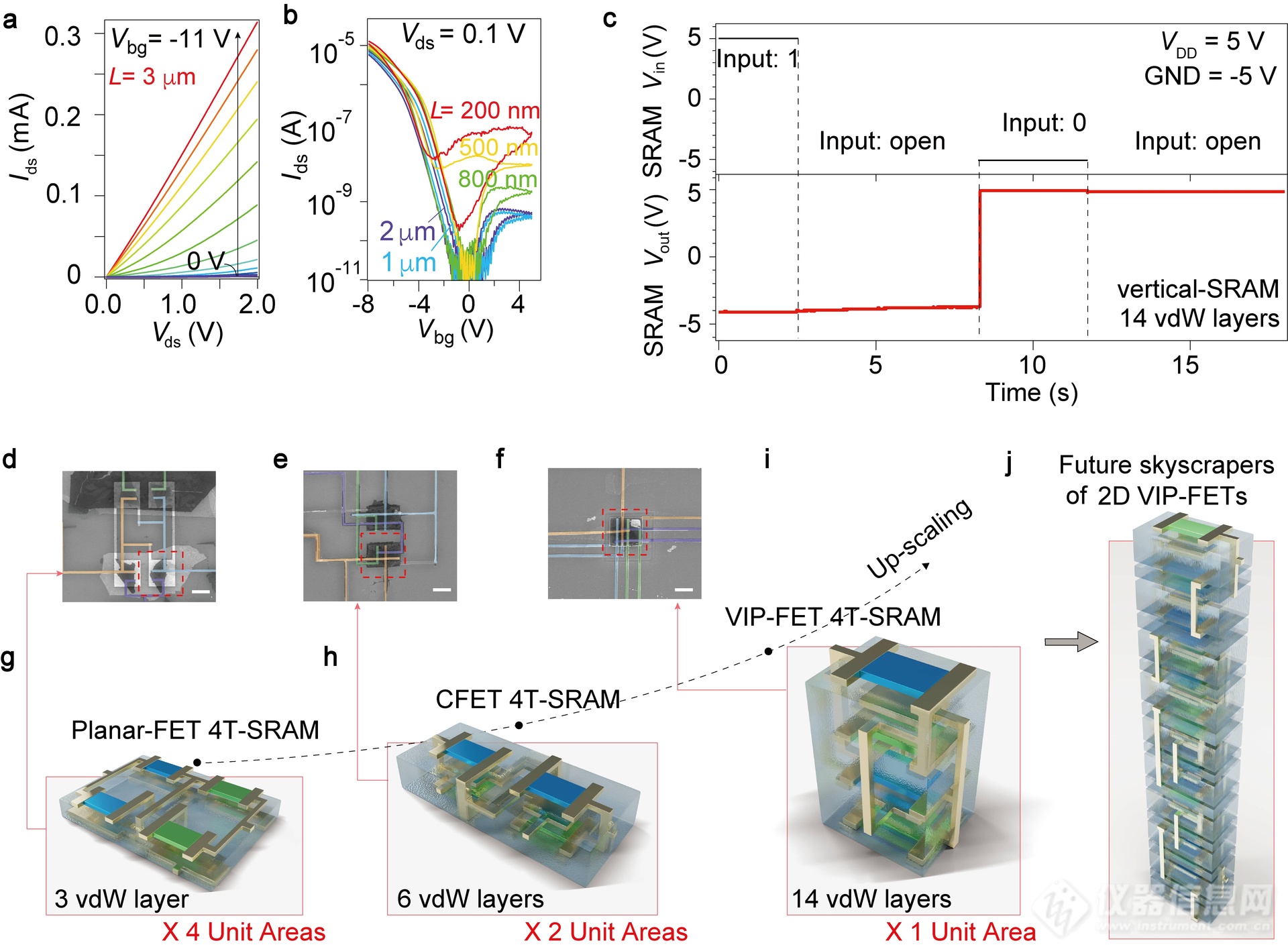

近日,中国科学院大学周武课题组与山西大学韩拯课题组、辽宁材料实验室王汉文课题组、中山大学候仰龙课题组、中国科学院金属所李秀艳课题组等合作,提出了一种全新的基于界面耦合的p型掺杂二维半导体方法。该方法采用界面效应的颠覆性路线,工艺简单、效果稳定,并且可以有效保持二维半导体本征的优异性能。在此基础上,该研究团队利用垂直堆叠的方式制备了由14层范德华材料组成、包含4个晶体管的互补型逻辑门NAND以及SRAM等器件(如下图所示)。这一创新方法打破了硅基逻辑电路的底层“封印”,基于量子效应获得了三维(3D)垂直集成多层互补型晶体管电路,为后摩尔时代未来二维半导体器件的发展提供了思路。

据“ 中国科学院大学”介绍,该掺杂策略预期可广泛适用于TMD材料与具有高功函数的层状绝缘体之间的界面,有望推动半导体电路先进三维集成的进一步发展。目前,该项由中国科学家主导的半导体领域新成果以“Van der Waals polarity-engineered 3D integration of 2D complementary logic”为题于2024年5月29日在Nature杂志在线发表。

原文链接:https://www.nature.com/articles/s41586-024-07438-5

[来源:仪器信息网] 未经授权不得转载

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~