【科学背景】

二维(2D)半导体具有原子级厚度,是潜在的高度缩放晶体管沟道材料,因其能够抑制短沟道效应而成为研究热点。然而,要超越传统的硅基晶体管,需要在2D半导体上开发无瑕的超薄高介电常数(κ)介电材料,以实现高效的栅极控制。

然而,由于2D半导体表面没有悬挂键,直接进行原子层沉积(ALD)来沉积介电层存在非均匀成核和电流泄漏的问题,特别是在介电层厚度小于3nm的情况下。为了解决这个问题,科学家们提出了多种界面工程方法,包括等离子预处理和种子层预沉积,但这些方法通常会引入额外的界面电荷散射、较差的热稳定性或整体栅极电容降低等问题。

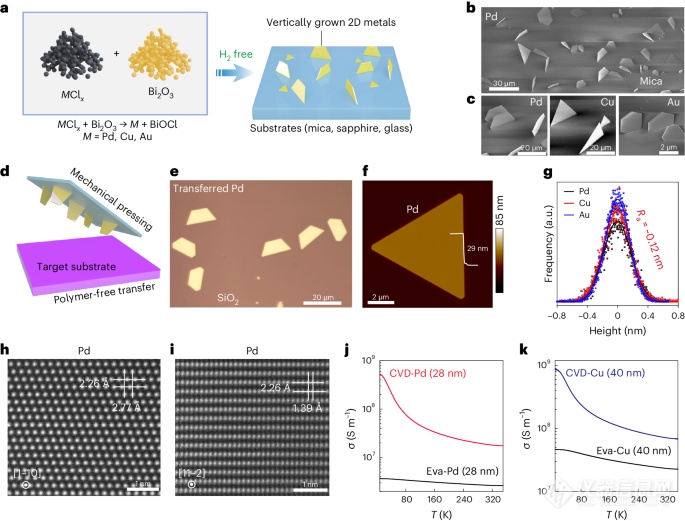

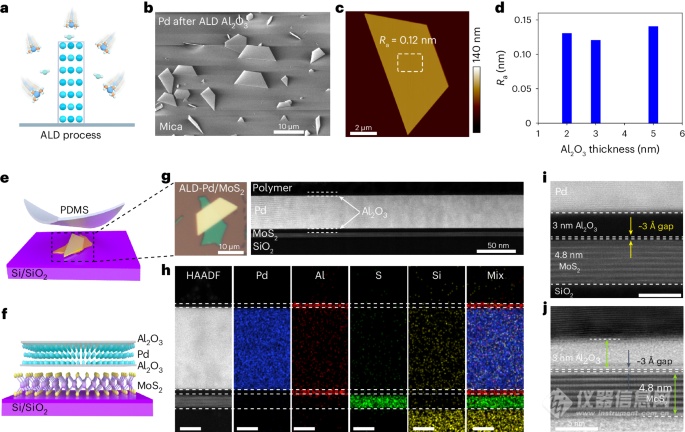

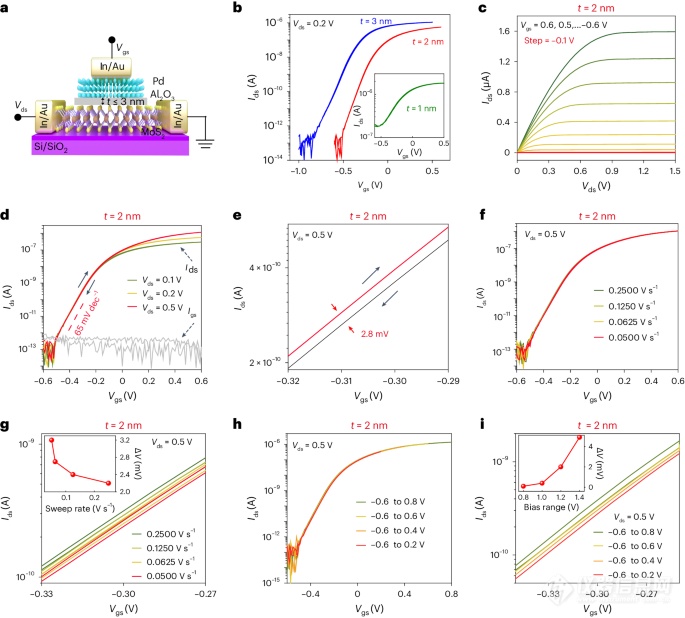

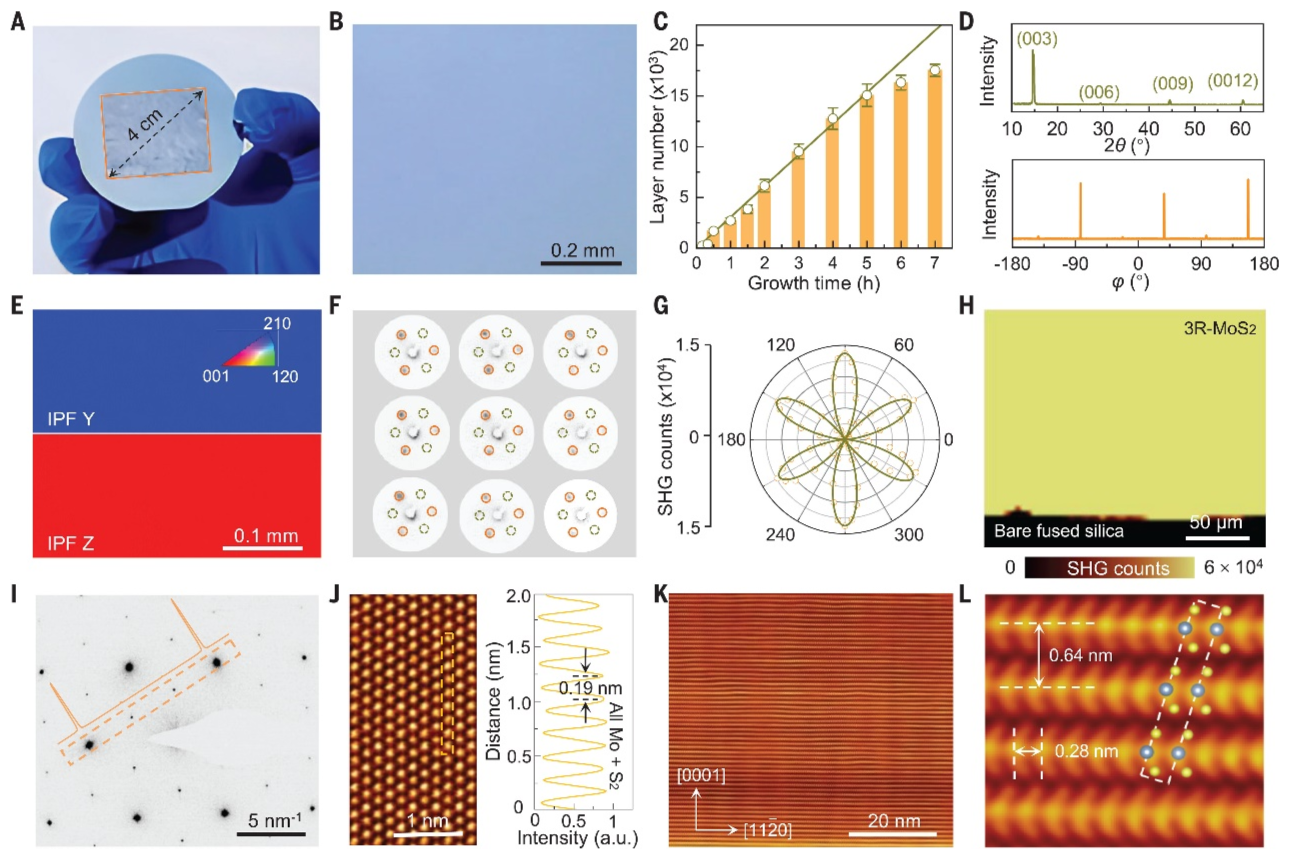

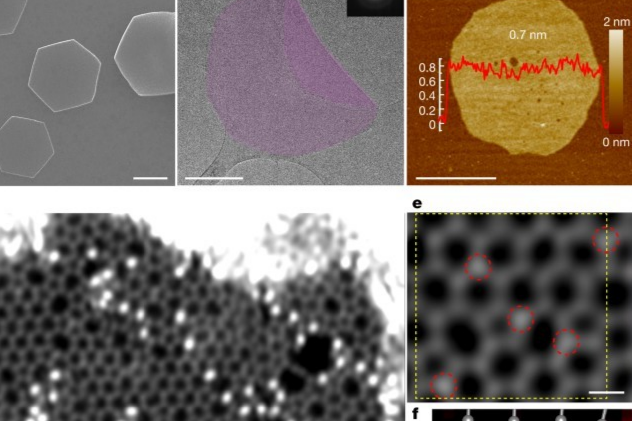

有鉴于此,南开大学材料科学与工程学院张磊,吴金雄等教授提出了一种垂直金属辅助的范德华(vdW)集成方法,这种方法能够在不损伤2D半导体表面的情况下,将高κ介电材料层叠到2D半导体上。研究中开发了一种铋氧化物(Bi2O3)辅助的化学气相沉积(CVD)方法,用于垂直生长钯、铜和金等单晶纳米片,这些纳米片具有原子级平整的表面。通过无聚合物的机械压合方法,这些纳米片可以轻松转移到目标基板上。此外,CVD生长的钯与ALD过程兼容,能够在其上沉积超薄高κ介电材料如Al2O3和HfO2,同时保持其原子级平整表面。

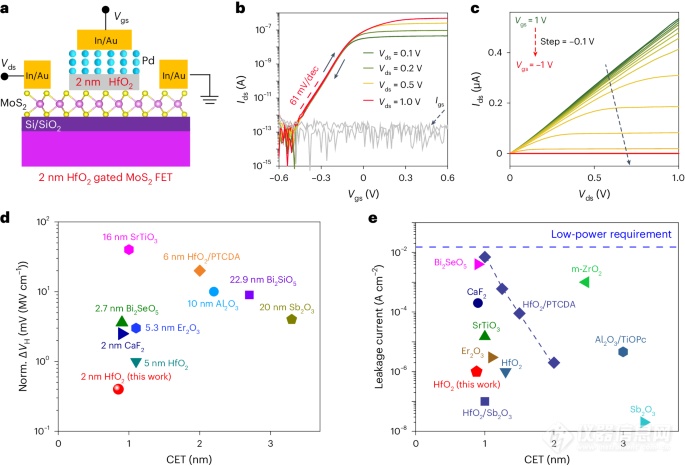

通过一步转移过程,研究人员将小于3nm的Al2O3/Pd和HfO2/Pd异质结构堆叠在几层的MoS2或石墨烯上,形成了清洁的vdW界面,没有有机污染或沉积引起的损伤。结果表明,使用2nm厚Al2O3或HfO2介电材料的顶栅MoS2场效应晶体管(FET)展示了约61mV/dec的亚阈值摆幅、0.45V的低工作电压、107的开/关比、10−6A/cm²的栅极漏电流和~1mV的可忽略滞后。

【科学亮点】

(1) 实验首次介绍了铋氧化物辅助化学气相沉积(CVD)方法:

• 首次开发了铋氧化物辅助CVD方法,用于垂直生长单晶金属纳米片,如钯、铜和金,这些纳米片具有原子级平整表面。

• 创新性地展示了纳米片通过无聚合物机械压合技术轻松转移到目标基板上,这一过程没有引入有机污染物,保持了原子级平整度。

(2) 实验通过vdW集成成功实现了亚1nm CEC的2D晶体管的制备:

• 使用了铋氧化物辅助CVD生长的钯纳米片作为基础,成功实现了超薄高介电常数(高κ)介电材料(如Al2O3和HfO2)的原子层沉积(ALD),保持了介电材料的原子级平整度。

• 在少层二硫化钼(MoS2)和石墨烯上,通过一步转移过程堆叠了小于3nm厚的Al2O3/Pd和HfO2/Pd异质结构,形成了清洁的vdW界面,避免了常见的沉积损伤和有机污染物的引入。

(3) 实验所制备的MoS2顶栅场效应晶体管(FET)展示了亚1nm CEC(0.9nm)的高介电常数(高κ)介电材料(Al2O3或HfO2)的优异性能。具体包括低至0.45V的操作电压、106 A/cm²的栅极漏电流。

【科学图文】

图1:垂直生长的单晶金属化学气相沉积chemical vapour deposition,CVD生长、无聚合物转移和表征。

图2:垂直生长钯Pd纳米片的原子层沉积atomiclayer deposition,ALD兼容性和范德华van der Waals,vDW集成。

图3:以亚3nm Al2O3/Pd作为顶栅介质和电极的MoS2晶体管。

图4:以2nm HfO2/Pd作为顶栅介质和电极的MoS2晶体管。

【科学结论】

本文的科学启迪在于了一种新颖的方法,利用铋氧化物辅助化学气相沉积(CVD)生长垂直单晶二维金属纳米片,并成功将其作为高质量原子层沉积(ALD)氧化物的平台。这一方法不仅解决了传统ALD技术在二维半导体表面上沉积难题,还避免了传统转移技术中介电层厚度过大的问题。通过铋氧化物的引入,实现了在原子级别上对金属表面的垂直生长,从而为超薄介电层的制备提供了一种新途径。

此外,本文还通过简化的一步法集成过程,成功在二维半导体上形成了范德华界面,避免了传统转移过程中的有机污染和损伤,确保了介电层的质量和性能。这不仅有助于在极小的电容等效厚度下实现高效的栅极控制,还为制造更高性能的二维场效应晶体管(FET)奠定了基础。

原文详情:Zhang, L., Liu, Z., Ai, W. et al. Vertically grown metal nanosheets integrated with atomiclayerdeposited dielectrics for transistors with subnanometre capacitanceequivalent thicknesses. Nat Electron (2024). https://doi.org/10.1038/s41928024012023

[来源:仪器信息网] 未经授权不得转载

2024.08.12

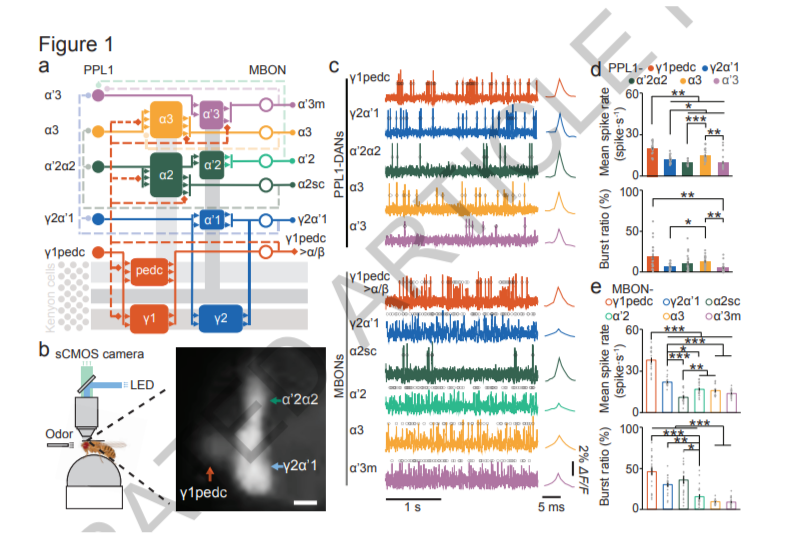

仪器新应用,科学家利用电压成像技术揭示多巴胺调控下的记忆网络机制!

2024.08.26

2024.08.26

2024.08.26

2024.08.26

2024.08.26

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~