近日,中国科大微电子学院胡诣哲与林福江课题组设计的一款基于全新电荷舵采样(Charge-SteeringSampling, CSS)技术的极低抖动毫米波全数字锁相环(CSS-ADPLL)芯片入选2023 Symposium on VLSI Technology and Circuits(以下简称VLSI Symposium)。VLSI Symposium是超大规模集成电路芯片设计和工艺器件领域最著名的国际会议之一,也是展现IC技术最新成果的橱窗,今年VLSI Symposium于6月11日至16日在日本京都举行。该论文第一作者为我校微电子学院博士生陶韦臣,胡诣哲教授为通讯作者。

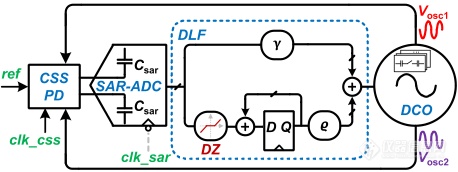

极低抖动毫米波频率综合器芯片是实现5G/6G毫米波通信的关键核心模块,为毫米波通信提供精准的载波信号。此研究提出的电荷舵采样技术,将电荷舵采样和逐次逼近寄存器型模数转换器(SAR-ADC)进行了巧妙的结合,构建了一种高鉴相增益,高线性度且具有多bit数字输出的数字鉴相器。CSS-ADPLL的结构十分紧凑(如图1所示),由电荷舵鉴相器(CSS-PD)、SAR-ADC、数字滤波器和数控振荡器组成,具有优异相位噪声性能,较快的锁定速度并消耗极低的功耗。

图1.论文提出的电荷舵采样全数字锁相环(CSS-ADPLL)架构

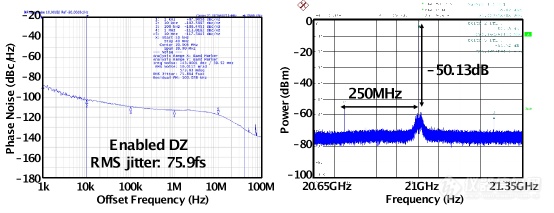

测试结果表明,该芯片实现了75.9fs的时钟抖动与–50.13dBc的参考杂散,并取得了-252.4dB的FoM值,为20GHz以上数字锁相环的最佳水平,芯片核心面积仅为0.044mm2。该研究成果以“An 18.8-to-23.3 GHz ADPLL Based on Charge-Steering-Sampling Technique Achieving 75.9 fs RMS Jitter and -252 dB FoM”为题由博士生陶韦辰在大会作报告。

图2.CSS-ADPLL相位噪声与参考杂散测试结果

该研究工作得到了科技部国家重点研发计划资助,也得到了中国科大微电子学院、中国科大信息科学技术学院支持。

[来源:中国科学技术大学]

2023.07.05

1141万!济南微生态生物医学省实验室和陕西省产品质量监督检验研究院仪器设备采购项目

2024.07.18

科学岛团队在微流控CRISPR-Dx检测流感病毒分型研究方面取得新进展

2024.07.03

2024.07.03

会议通知丨第十一届中国微流控高端学术论坛 暨第四届国际微流控产业论坛 第一轮通知

2024.05.22

再添“芯”认证!睿创微纳8微米红外热成像芯片再获AECQ车规认证

2024.05.15

版权与免责声明:

① 凡本网注明"来源:仪器信息网"的所有作品,版权均属于仪器信息网,未经本网授权不得转载、摘编或利用其它方式使用。已获本网授权的作品,应在授权范围内使用,并注明"来源:仪器信息网"。违者本网将追究相关法律责任。

② 本网凡注明"来源:xxx(非本网)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。如其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

③ 如涉及作品内容、版权等问题,请在作品发表之日起两周内与本网联系,否则视为默认仪器信息网有权转载。

![]() 谢谢您的赞赏,您的鼓励是我前进的动力~

谢谢您的赞赏,您的鼓励是我前进的动力~

打赏失败了~

评论成功+4积分

评论成功,积分获取达到限制

![]() 投票成功~

投票成功~

投票失败了~