Nature最新进展:DNA折纸术搭档二氧化硅,随心所欲搭积木!

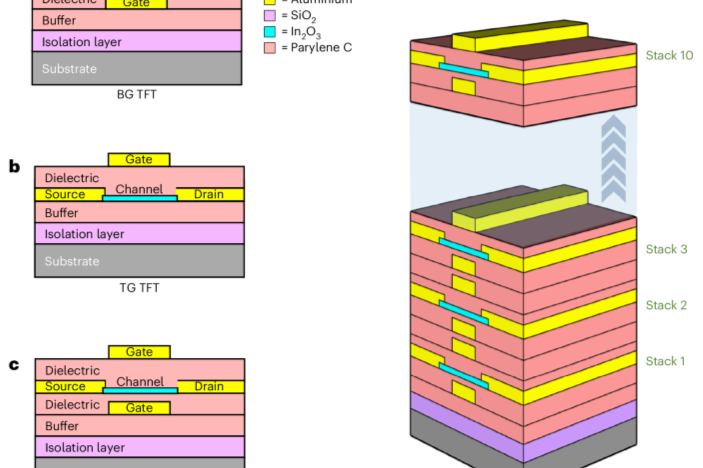

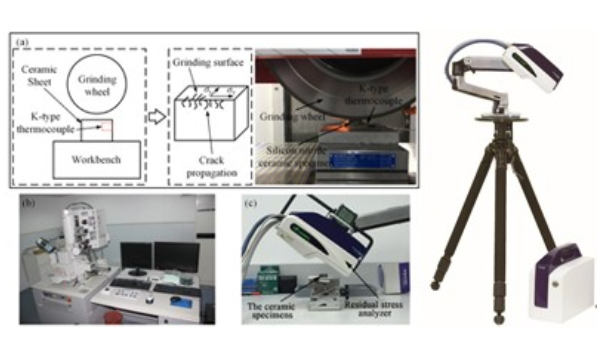

p span style=" color: rgb(255, 0, 0) " strong span style=" font-size: 18px " 前言 /span /strong /span /p p style=" line-height: 1.5em " DNA折纸术是最近十多年流行起来的纳米合成的高级玩法。 /p p style=" line-height: 1.5em " 北京时间2018年7月17日凌晨,Nature在线发表了来自中国科学院上海应用物理研究所、上海交通大学和美国Arizona State University等多家科研单位合作的成果,作者受自然界广泛存在的硅藻启发,成功地实现了具有SiO sub 2 /sub 层包覆的DNA折纸纳米组装策略(Nature, 2018, doi:10.1038/s41586-018-0332-7)。 /p p style=" line-height: 1.5em " span style=" color: rgb(31, 73, 125) " 第一作者 /span :Xiaoguo Liu, Fei Zhang, Xinxin Jing /p p style=" line-height: 1.5em " span style=" color: rgb(31, 73, 125) " 通讯作者 /span :Hao Yan和樊春海 /p p style=" line-height: 1.5em " span style=" color: rgb(31, 73, 125) " 第一单位 /span :中国科学院上海应用物理研究所 /p p style=" text-align: center " img src=" http://img1.17img.cn/17img/images/201807/insimg/65a91c76-9779-44bd-849d-01aebd0aef9c.jpg" title=" QQ截图20180717103638.png" / /p p span style=" font-size: 18px color: rgb(255, 0, 0) " strong span style=" font-size: 18px " 课题背景介绍 /span /strong /span /p p style=" line-height: 1.5em " span style=" font-size: 18px " & nbsp & nbsp & nbsp & nbsp span style=" font-size: 16px " DNA的双螺旋结构,因为四个碱基单元特异性配对,两条单链的独特结构,这使得DNA的自组装玩出了很多高级花样。 /span /span /p p style=" line-height: 1.5em text-align: center " span style=" font-size: 16px " img src=" http://img1.17img.cn/17img/images/201807/insimg/ae291e3f-d5c2-48a0-8ac8-781449b93126.jpg" title=" 微信图片_20180717101902.jpg" / /span /p p style=" text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " 2006年DNA二维折纸术的横空出世(Paul W. K. Rothemund, Nature 2006, 440, 297) /span /p p style=" text-align: center " br/ /p p style=" text-align: center " img src=" http://img1.17img.cn/17img/images/201807/insimg/fb8ee97e-6e1d-42f2-ad59-e47b2ae12861.jpg" title=" 微信图片_20180717101906.jpg" / /p p style=" text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " 2017年DNA产生的二维折纸,已经到达了微米级。借助于编程,可以产生蒙娜丽莎的微笑。(Tikhomirov, G. et al. Nature(2017) 552, 67.) /span /p p span style=" color: rgb(0, 0, 0) " & nbsp & nbsp & nbsp & nbsp 还可以这样玩: /span span style=" color: rgb(31, 73, 125) " br/ /span /p p style=" text-align: center " span style=" color: rgb(0, 0, 0) " img src=" http://img1.17img.cn/17img/images/201807/insimg/2558ca78-6e18-4803-8864-89c5df940c07.jpg" title=" 微信图片_20180717101910.jpg" / /span /p p style=" text-align: center " span style=" font-size: 14px color: rgb(31, 73, 125) " DNA折纸的中国地图图样,(QIAN Lulu等, Chinese Science Bulletin 2006 Vol. 51 No. 24 2973—2976) /span /p p style=" line-height: 1.5em " & nbsp & nbsp & nbsp & nbsp 虽然图样控制已经接近随心所欲的水平,但是DNA纳米技术还需要找到合适的应用出口。与氧化物的复合是一种理想的策略。但是 span style=" color: rgb(31, 73, 125) " strong DNA折纸得到的纳米结构需要很高的离子浓度(如Mg)以维持稳定,这使得其它组分在DNA组装体的进一步沉积变得困难 /strong /span 。 /p p style=" line-height: 1.5em " 今天这篇Nature 文章在实现DNA表面的包覆SiO2层可控的包覆的同时,依然保持着DNA的复杂组装图案,并有效提高组装体的稳定性,作者将这种新的DNA折纸玩法称为:DNA硅化折纸术,DNA origami silicification (DOS)。 /p p style=" line-height: 2em " span style=" color: rgb(255, 0, 0) " strong span style=" font-size: 18px " 全文亮点 /span /strong /span /p p style=" line-height: 1.5em " 1. 基于分子动力学模拟的结果,将两种硅和磷酸前躯体的预先团聚策略,使得硅源成功地沉积到DNA骨架的表面中,实现了DNA-SiO2的复合结构构筑。 /p p style=" line-height: 1.5em " 2. 利用此策略,基于各种DNA折纸模板,合成了一维、二维和三维的多层级纳米组装体,其尺寸在10到1000nm。 /p p style=" line-height: 1.5em " 3. 无定型SiO2层厚度可随生长时间调节。 /p p style=" line-height: 1.5em " 4. DNA-SiO2的杂化结构稳定性提高十倍。 /p p style=" line-height: 2em " span style=" font-size: 18px color: rgb(255, 0, 0) " strong 图文快解 /strong /span /p p style=" line-height: 2em text-align: center " span style=" font-size: 18px color: rgb(255, 0, 0) " strong img src=" http://img1.17img.cn/17img/images/201807/insimg/45a432ae-823a-4f1b-be92-819f84268954.jpg" title=" QQ截图20180717103936.png" / /strong /span /p p span style=" font-size: 14px color: rgb(31, 73, 125) " span style=" font-size: 16px color: rgb(0, 0, 0) " /span /span /p p style=" text-align: center line-height: 1.5em " span style=" font-size: 14px color: rgb(31, 73, 125) " 图1 DNA硅化折纸术,DNA origami silicification (DOS)的实现示意图。 /span /p p style=" line-height: 1.5em " 要点:分子动力学模拟启发,TMAPS和TEOS两种前躯体预先组成小团簇,然后就可以沉积于DNA组装体的表面。 /p p style=" line-height: 1.5em text-align: center " img src=" http://img1.17img.cn/17img/images/201807/insimg/30b14b15-aa47-406a-a25c-9267fd46cf50.jpg" title=" QQ截图20180717103959.png" / /p p style=" line-height: 1.5em text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " 图2 DOS组装体的几何结构控制。 /span /p p style=" line-height: 1.5em text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " img src=" http://img1.17img.cn/17img/images/201807/insimg/535924d4-8dc4-4a7c-9b48-7b9904386aa4.jpg" title=" QQ截图20180717105304.png" / /span /p p style=" line-height: 1.5em text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " 图3 复杂结构也无压力 /span /p p style=" line-height: 1.5em " 要点:EDS显示Si/O/P的均匀分布。 /p p style=" line-height: 1.5em text-align: center " img src=" http://img1.17img.cn/17img/images/201807/insimg/937c9812-814c-49df-a0f7-9e5ce7c32ca4.jpg" title=" QQ截图20180717105425.png" / /p p style=" line-height: 1.5em text-align: center " span style=" color: rgb(31, 73, 125) font-size: 14px " 图4 DOS结构的纳米机械性能。 /span /p p style=" line-height: 1.5em " 要点:a,五天的硅化反应后,DOS三角形的杨氏模量比传统的DNA折纸结构提高十倍。c,利用AFM tip挤压DOS四面体考察其变形性。 /p p style=" line-height: 1.5em " f:将两个Au纳米棒组装到四面体的两条棱边上,硅化的DOS组装体刚性更好。 /p p style=" line-height: 1.5em " br/ /p p style=" line-height: 1.5em " 总而言之,考虑到SiO2-DNA复合结构可以当做更好的三维载体,这项工作最终可能在新的光学系统、半导体纳米组成、纳米电子、纳米机器人和包括药物输送在内的医疗应用领域具有广阔的应用前景。 /p p style=" line-height: normal " span style=" font-size: 14px color: rgb(31, 73, 125) " br/ /span br/ /p p br/ /p