前沿科技 | 半导体先进封装,其实离我们不遥远

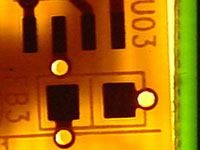

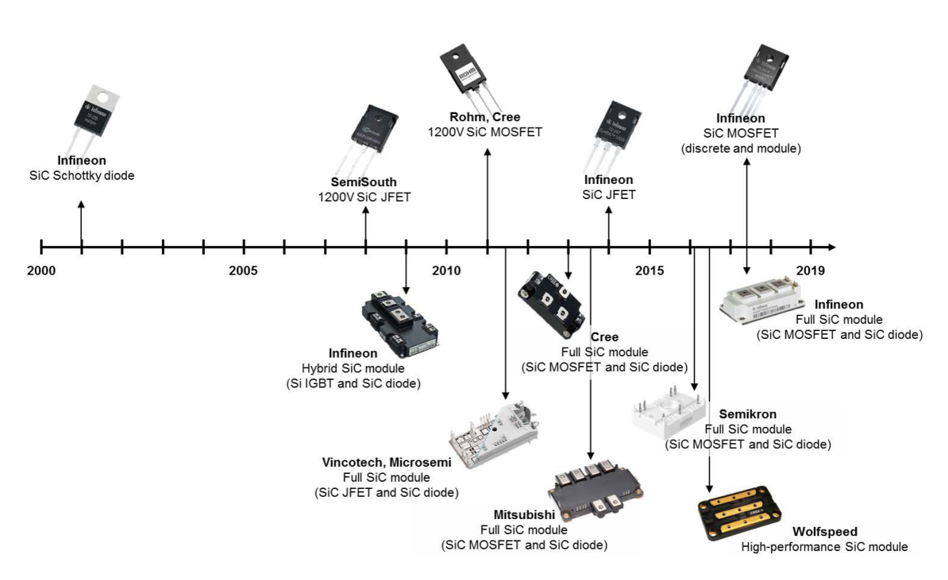

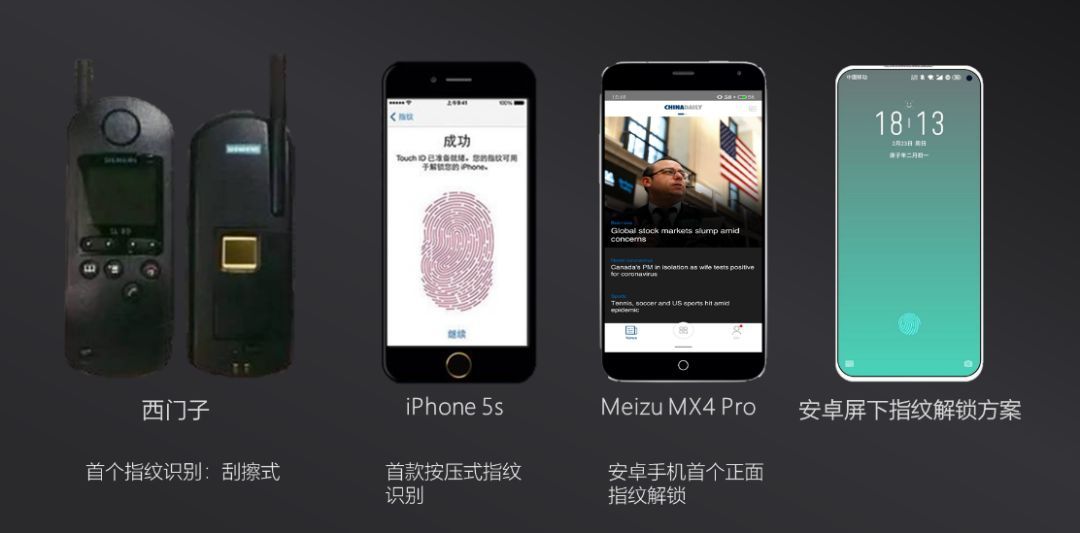

如果列举一下当代智能手机的几大前沿技术,那么屏幕下指纹识别一定在列。之所以这样笃定,是因为它不仅带来了全新的交互解锁方式,更是手机迈向「全面屏」时代的一次重大技术飞跃。或许你会说,苹果的Face ID人脸识别解锁方式不也同样“真香”吗?但此类方案不可避免的要保留住“刘海”。所以,包括苹果在内,将来手机的发展方向,一定是「真」全面屏的时代,或许在不远的未来,我们可以看到更富有科技感的屏幕下摄像头的技术方案。那么大家有没有想过,是什么促使近些年手机发展的这么迅速?除了半导体制造工艺的改进,我想,更重要的原因,是以WLP(晶圆级封装)和TSVs(硅通孔)为代表的先进封装技术的应用。这些所谓先进封装技术究竟是什么意思?对我们的日常生活有什么影响?在这里小编先卖个关子,想要说清这个问题,还需要从半导体制造和封装技术的起源和演变说起。摩尔定律:半导体工艺的基础1965年,时任仙童半导体公司的Gordon Moore在《Electronics》杂志上第一次提出,一块芯片上集成的晶体管和其他元器件的数量,当价格不变时,约每隔18-24个月便会增加一倍,性能也将提升一倍,这就是著名的摩尔定律。随后便是50多年的工艺提升,半导体的制程技术,在摩尔定律的加持下,呈现指数增长的态势,凭借光刻技术的发展,从上世纪80年代还是微米量级的制程水准,迸发到如今英特尔和台积电可以量产的7nm时代,甚至计划在2025年的3nm工艺,进步可谓“触目惊心”,然而,这种状态不可能无穷无尽下去,普遍认为在7nm技术节点后,摩尔定律将迎来失效… … 摩尔定律的失效:半导体制造技术的瓶颈让我们想象一下,在标准的8人百米跑道上,大家可以相安无事的相互角逐,但如果这个跑道宽度没有变化,而人数增加了,变成了16个人,此时还能够大幅摇摆,没有相互影响吗?ok,你说运动员身体宽度太大,换成小孩子不就可以了吗?那这个人数变成了32、64… 呢?无论是谁在比赛跑道上,当数量增加到一定程度,而跑道宽度没变,甚至还需要缩小的时候,总要有个物理极限,在这个极限,就是摩尔定律失效的主要原因之一。纵使技术上能够实现,芯片内集成电路的两条导线也不可能无限接近。因为两个导线的距离过近会导致「量子跃迁」,也就是说,一条导线上的电子会越过中间的绝缘体跑到另一条导线上,造成电路失效。从另一个维度来看,摩尔定律难以维系的重要原因,是纳米芯片制造的资金壁垒高的离谱,一条28nm工艺制程芯片生产线的投资额大约是50亿美元,20nm的高达100亿美元,随着制程工艺升级换代,生产线投资呈几何级飙升,单单是一台极紫外光刻机(EUV)的售价,就将近10亿元人民币。后摩尔定律时代:新技术路线的开拓单纯地减小晶体管(MOS)尺寸,在技术和成本上实现的难度非常高,但是,延续摩尔定律并不是只有一条路可以走。以3D封装为代表的先进封装技术,在不缩减工艺尺寸的前提下,增加了chip(器件单元)集成度从而提升性能并缩减成本,这种技术路线被称为新摩尔定律(More than Moore)。举个例子,传统封装先将晶圆Wafer切割成小的单元Chip,然后再逐个封装;而新的WLP晶圆级封装(Wafer-Level Package)是在整片晶圆上进行封装和测试,然后再切割成一个个的IC Chip。相比于传统封装,新的WLP封装流程有着肉眼可见的优势:① 省去了引线键合,封装后的体积即等同IC裸晶的原尺寸,Wafer面积不变,可同时封装更多的芯片,提升了集成度;②减少了测试和封装工序,有效地降低了成本;③降低芯片的贴装高度,跟进了数码产品日益变薄的需求。 * 晶圆级封装(WLP)流程(Brewer science官网)其实,上述的例子与我们消费者并不遥远,有感于近些年手机等数码产品的性价比的提升,封装成本的降低功不可没;如果说,有哪种封装技术的进步,是与我们息息相关的,毫无疑问的要属TSVs(硅通孔)封装形式的开发和应用。TSV封装技术及其失效分析在三维封装中,封装形式逐渐由Wire bonding转向TSVs,技术的革新,突出的外化表现是手机指纹解锁方式的改变,即iPhone 5s为代表的电容式Home键指纹解锁,转向安卓全面屏手机的屏下指纹解锁。上图中,是iPhone 5s为代表的电容式指纹解锁,采用Wire bonding式3D封装,表面开孔,手指与盖板(玻璃、蓝宝石、陶瓷)直接接触,而在芯片一端,需要进行塑封处理,将金属引线掩埋,形成平整的表面。其原理是依据指纹在盖板上按压时,会形成高低不平(肉眼不可见),这时候传感器会记下指纹的形状,以供日后解锁使用。 然而,随着智能手机向「厚度更薄、屏占比更高」的方向发展,wire bonding封装方式的缺点逐渐凸显:键合线容易造成短路,虚焊、脱焊等封装不良问题,塑封处理导致芯片无法进一步变薄,最致命的,如果把这种封装芯片放在屏幕下方,隔着一层屏幕模组会导致传感器收集不到足够的指纹信号,无法顺利完成解锁。好在TSV新型封装的出现解开了这种困局,所谓TSV,又称硅通孔,指的是在芯片3D晶圆级封装的基础上,在芯片间或晶圆间制作垂直通道,实现芯片间的垂直互联,具有高密度集成、电性能提升等优点。 目前市面上的主流手机,几乎清一色的采用了OLED和AMOLED屏幕,除了苹果,均采用了屏幕下指纹解锁技术,而OLED屏幕面板能够「霸屏」全面屏的旗舰机,其成功是离不开TSV封装的。所谓的OLED,其工作原理是利用了光的折射和反射,当手指按压屏幕时,OLED面板的每个像素点能够自主发光,照亮指纹的反射光线透过OLED层像素的间隙返回到紧贴于屏下的传感器芯片上,获取的指纹图像与手机初次录入的图像进行对比,最后进行识别判断,完成解锁。OLED能够顺利完成解锁,依据的就是下方传感器能够无衰减的接受反射信号,试想一下,如果在芯片表面盖了一层盖子(塑封胶体),识别率会大打折扣,所以,TSV结构是完成该解锁技术的关键。除此之外,TSV封装还可以有效的减小封装厚度,顺应了数码产品变薄的潮流:三星电子在2006年成功将TSV技术应用在晶圆级堆叠封装16Gb NAND闪存芯片中,将系统厚度减薄了160μm。系统集成度越高,相应的失效问题越多,失效分析的难度也就越高,TSV也不例外。传统的Wire bonding堆叠,失效多集中在键合线和焊点处,相比于TSV封装,更加的「宏观化」,而TSV结构更微观,并且大量的失效不良,多集中在内部通孔,对技术人员和检测设备都提出了更高的要求。TSV内部通孔需要电镀Cu,而Cu的生长过程是自下而上进行的,并且生长过程所需要的促进剂和抑制剂消耗不均匀,通常抑制剂在底部先消耗,于是底部的促进剂发挥主要作用;再由于有机物的抑制剂中,高浓度的Cl、N、O杂质元素大量分布在晶界上,通过钉扎效应(Zener pinning)对晶粒的自由生长起进一步的抑制作用,导致顶部的Cu晶粒较小,最终在通孔内部形成了内应力,导致裂纹、胀出等不良现象。 * TSV通孔内部晶粒尺寸对比 & 空洞、裂纹、填充缺失典型缺陷结语 & 后续预告半导体先进封装技术的迅猛发展惠及了我们的日常生活,然而对于半导体的从业者,这一切来的并不容易,先进且更复杂的结构拔高了不良分析的门槛值,文章中列举的案例都是通过大面积截面抛光,再辅以SEM观察,而在更多的失效分析中,通常是需要利用FIB进行某(数)个TSV孔进行定点切割分析,所以在半导体封装产线高时效性要求的背景下,从制样到成像的分析效率就显得格外重要,众所周知,FIB是定点分析的利器,但效率不高也是普遍存在的通病,所以,后续内容中,我们会介绍一款超高效率的激光刻蚀设备microPREP,辅助FIB,可以显著缩短整个失效分析的周期,敬请期待!参考文献:[1] T.Frank, S.Moreau, C.Chappaz, L.Arnaud, P.Leduc, A.Thuaire. Electromigration behavior of 3D-IC TSV interconnects[C]. 2012 IEEE and Electronic Components and Technology Conference (ECTC), 2012, 326-330.[2] 程万. 高深比的TSV电镀铜填充技术研究. 中国科学院大学,2017[3] KANG U, CHUNG H J, HEO S, PARK D H, LEE H, KIM J H, LEE J W. 8 Gb 3-D DDR3 DRAM using through-silicon-via technology[J]. IEEE Journal of Solid-State Circuits, 2010, 45(1): 111-119.[4] OKORO C, LABIE R, VANSTREELS K, FRANQUET A, GONZALEZ M, VANDEVELDE B, VERLINDEN B. Impact of the electrodeposition chemistry used for TSV filling on the microstructural and thermo-mechanical response of Cu[J]. Journal of Materials Science, 2011, 46(11): 3868-3882.