如何精准找出CIS影像晶片缺陷?透过量子效率光谱解析常见的4种制程缺陷!

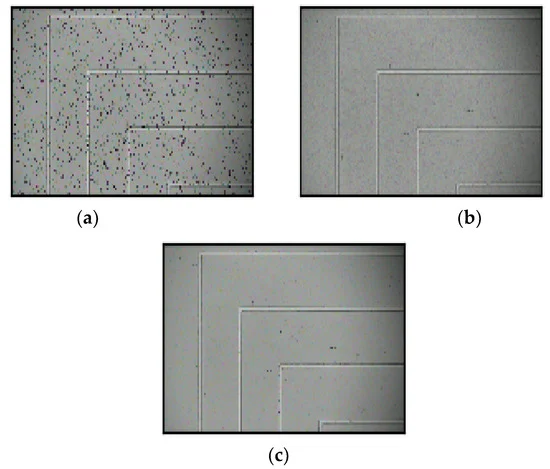

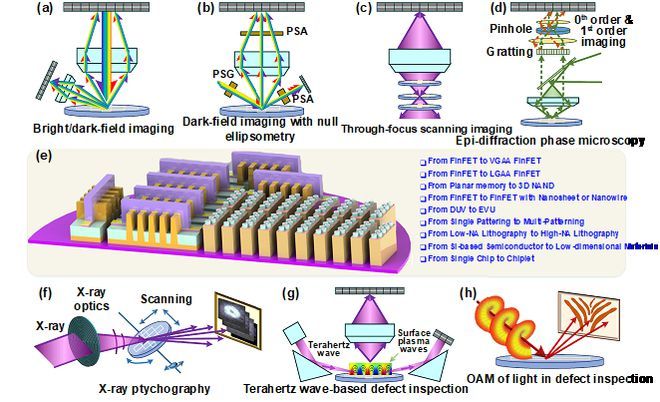

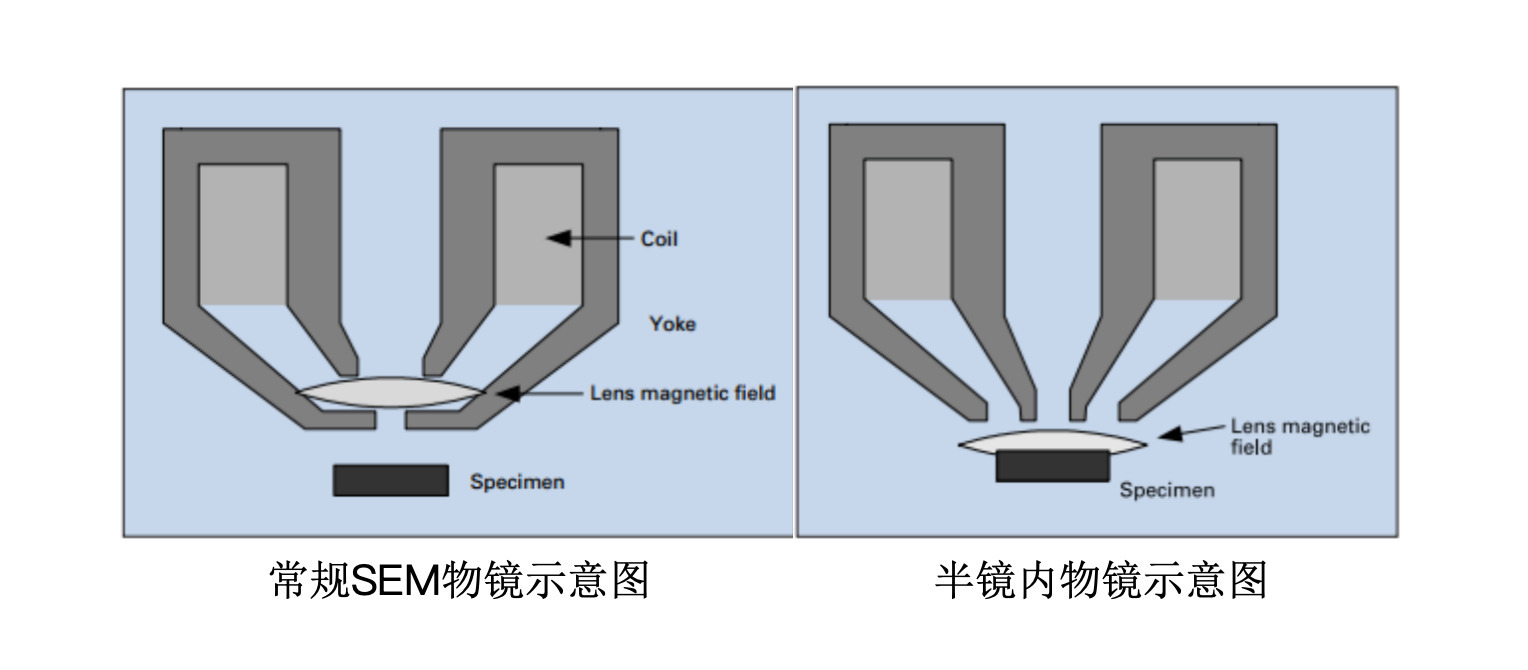

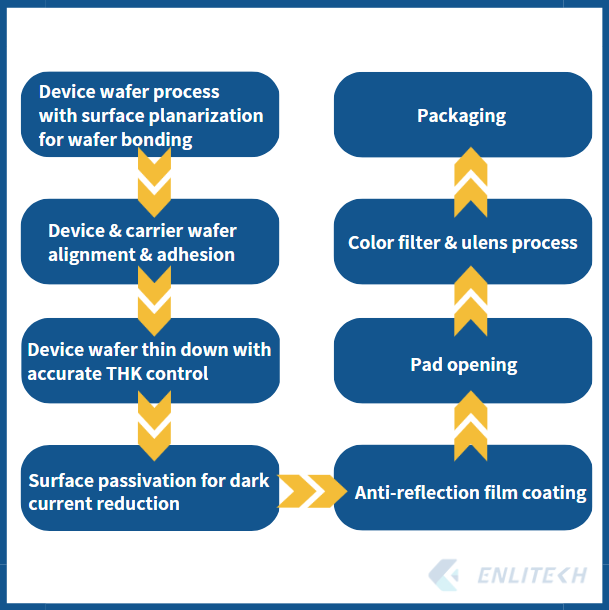

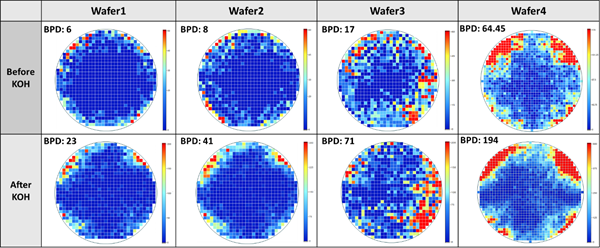

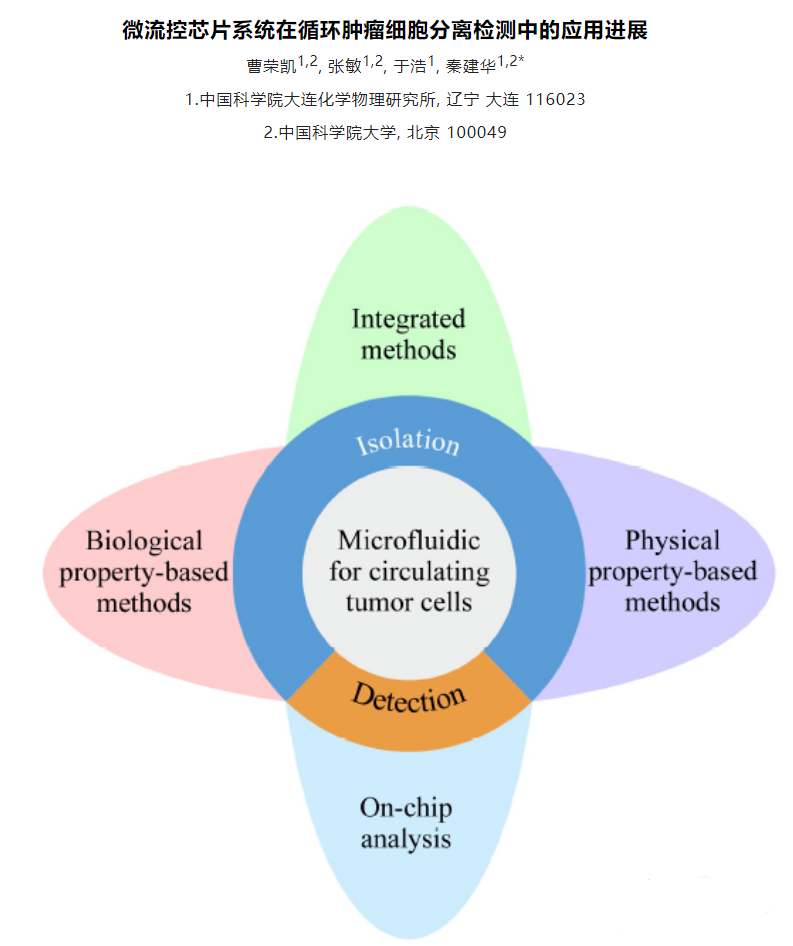

本文将为您介绍何谓量子效率光谱,以及CIS影像晶片常见的4种制程缺陷。SG-A_CMOS 商用级图像传感器测试仪相较于传统光学检测设备可以提供更精细的缺陷检测资讯,有助于使用者全面了解CIS影像晶片的性能表现。量子效率光谱是CIS影像晶片的关键参数之一,可以反映CIS影像晶片对不同波长下的感光能力,进而影响影像的成像质量。1. 什么是CIS影像晶片的量子效率光谱?CIS影像晶片的量子效率光谱是指在不同波长下,CIS晶片对光的响应效率。物理上,光子的能量与其波长成反比,因此,不同波长的光子对CIS影像晶片产生的响应效率也不同。量子效率光谱可以反映传感器在不同波长下的响应能力,帮助人们理解传感器的灵敏度和色彩还原能力等特性。通常,传感器的量子效率光谱会在可见光波段范围内呈现出不同的特征,如波峰和波谷,这些特征也直接影响着传感器的成像质量。2. Quantum Efficiency Spectrum 量子效率光谱可以解析CIS影像晶片内部的缺陷,常见的有下四种:BSI processing designOptical Crosstalk inspectionColor filter quality and performanceSi wafer THK condition in BSI processing3. 透过量子效率光谱解析常见的4种制程缺陷A. 什么是BSI制程?(1) BSI的运作方式BSI全名是Back-Side Illumination.是指"背照式"影像传感器的制造工艺,它相对于传统的"正面照射"(FSI, Front-Side Illumination)影像传感器,能够提高影像传感器的光学性能,特别是在各波长的感光效率的大幅提升。在BSI制程中,像素置于矽基板的背面,光通过矽基板进入感光像素,减少了前面的传输层和金属线路的干扰,提高了光的利用率和绕射效应,进而提高了影像传感器的解析度和灵敏度。(2) 传统的"正面照射"(FSI, Front-Side Illumination)图像传感器的工作方式FSI 是一种传统的图像传感器制程技术,光线透过透镜后,从图像传感器的正面照射到图像传感器的感光面,因此需要在感光面(黄色方框, Silicon)的上方放置一些电路和金属线,这些元件会遮挡一部分光线,降低图像传感器的光量利用率,影响图像的品质。相对地,BSI 技术是在感光面的背面,也就是基板反面制作出感光元件,让光线可以直接进入到感光面,这样就可以最大限度地提高光量利用率,提高图像的品质,并且不需要额外的电路和金属线的遮挡,因此也可以实现更高的像素密度和更快的图像读取速度。(3) 为什么BSI工艺重要?BSI工艺是重要的制造技术之一,可以大幅提升CIS图像传感器的感光度和量子效率,因此对于低光照环境下的图像采集有很大的帮助。BSI工艺还可以提高图像传感器的分辨率、动态范围和信噪比等性能,使得图像质量更加优良。由于现今图像应用日益广泛,对图像质量和性能要求也越来越高,因此BSI工艺在现代图像传感器的制造中扮演着重要的角色。目前,BSI 技术已成为图像传感器的主流工艺技术之一,被广泛应用于各种高阶图像产品中。(4) 量子效率光谱如何评估BSI工艺的好坏如前述,在CIS图像芯片的制造过程中,不同波长的光子对于图像芯片的感光能力有所不同。因此,量子效率光谱是一种可以检测图像芯片感光能力的方法。利用量子效率光谱,可以评估BSI工艺的好坏。Example-1如图,TSMC使用量子效率光谱分析了前照式FSI和背照式BSI两种工艺对RGB三原色的像素感光表现的差异。结果表明,BSI工艺可以大幅提高像素的感光度,将原本FSI的40%左右提高到将近60%的量子效率。上图 TSMC利用Wafer Level Quantum Efficiency Spectrum(量子效率光谱)分析1.75μm的前照式FSI与背照式BSI两种工艺对RGB三原色的像素在不同波长下的感光表现差异。由量子效率光谱的结果显示,BSI工艺可以大幅提升像素的感光度,将原本FSI的40%左右提高到将近60%的量子效率。(Reference: tsmc CIS)。量子效率光谱的分析可以帮助工程师判断不同工艺对感光能力的影响,并且确定BSI工艺的优势。(5) 利用量子效率光谱分析不同BSI工艺工艺对CIS图像芯片感光能力的影响Example-2 如上图。Omnivision 采用Wafer Level Quantum Efficiency Spectrum量子效率光谱分析采用TSMC 65nm工艺进行量产时,不同工艺工艺,对CIS图像芯片感光能力的影响。在1.4um像素尺寸使用BSI-1工艺与BSI-2的量子效率光谱比较下,可以显著的判断,BSI-2的量子效率较BSI-1有着将近10%的量子效率提升。代表着BSI-2的工艺可以让CIS图像芯片内部绝对感光能力可以提升10%((a)表)。此外,量子效率光谱是优化CIS图像芯片制造的重要工具。例如,在将BSI-2用于1.1um像素的工艺中,与1.4um像素的比较表明,在蓝光像素方面,BSI-2可以提供更高的感光效率,而在绿光和红光像素的感光能力方面,BSI-2的效果与1.4um像素相似。另外,Omnivision也利用量子效率光谱分析了TSMC 65nm工艺中不同BSI工艺工艺对CIS图像芯片感光能力的影响,发现BSI-2可以提高近10%的量子效率,从而使CIS图像芯片的感光能力提高10%。将BSI-2工艺用于1.1um像素的制造,并以量子效率光谱比较1.4um和1.1um像素。结果显示,使用BSI-2工艺的1.1um像素,在蓝色像素方面具有更高的感光效率,而在绿色和红色像素的感光能力方面与1.4um像素相近。这个结果显示,BSI-2工艺可以在保持像素尺寸的前提下提高CIS图像芯片的感光能力,进而提高图像质量。因此,利用量子效率光谱比较不同工艺工艺对CIS图像芯片的影响,可以为CIS制造优化提供重要参考。上图 Omnivision采用了Wafer Level Quantum Efficiency Spectrum量子效率光谱,以分析TSMC 65nm工艺在量产时,不同工艺工艺对CIS图像芯片感光能力的影响。通过这种光谱分析技术,Omnivision能够精确地判断不同工艺工艺所产生的量子效率差异,并进一步分析出如何优化CIS图像芯片的感光能力。因此,Wafer Level Quantum Efficiency Spectrum量子效率光谱分析是CIS工艺中一项重要的技术,可用于协助提高CIS图像芯片的质量和性能。(Reference: Omnivision BSI Technology.)B. Optical Crosstalk Inspection(1) 什么是Optical Crosstalk?CIS的optical cross-talk是指光线在图像芯片中行进时,由于折射、反射等原因,导致相邻像素之间的光相互干扰而产生的一种影响。(2) 为什么Optical Crosstalk的检测重要?在CIS图像芯片中,optical crosstalk是一个重要的问题,因为它会影响图像的品质和精度。optical crosstalk是由于像素之间的光学相互作用而产生的,导致相邻像素的光信号互相干扰,进而影响到像素之间的区别度和对比度。因此,降低optical cross-talk是提高CIS图像芯片品质的重要目标之一。(3) 如何利用QE光谱来检测CIS 的Crosstalk?量子效率(QE)光谱可用于检测CMOS图像传感器(CIS)的串音问题。通过测量CIS在不同波长下的QE,可以检测CIS中是否存在串音问题。当CIS中存在串音问题时,在某些波长下可能会观察到QE异常。在这种情况下,可以采取相应的措施来降低串音,例如优化CIS设计或改进工艺。缩小像素尺寸对于高分辨率成像和量子图像传感器是绝对必要的。如上图,TSMC利用45nm 先进CMOS工艺,来制作0.9um 像素用于堆叠式CIS。而optical crosstalk光学串扰对于SNR与成像品质有着显著的影响。因此,TSMC采用了一种像素工艺,来改善这种optical crosstalk光学串扰。结构如下图。结构(a)是控制像素。光的路径线为ML(Microlens)、CF (Color Filter)、PD(Photodiode, 感光层)。而在optical crosstalk影响的示意图,如绿色线的轨迹。光子由相邻的像素单元进入后,因为多层结构的折射,入射到中间的PD感光区,造成串扰讯号。TSMC设计结构(b) “深沟槽隔离(DTI)" 技术是为了在不牺牲并行暗性能的情况下抑制光学串扰。由(b)可以发现,DTI所形成的沟槽可以隔离原本会产生光学串扰的光子入射到中间的感光Photodiode区,抑制了串扰并提高了SNR。像素的横截面示意图 (a) 控制像素 (b)串扰改善像素。Wafer Level Quantum Efficiency Spectrum of two different structure CISs. 在该图中,展示了0.9um像素的量子效率光谱,其中虚线代表控制的0.9um像素(a),实线代表改进的0.9um像素(b)。由于栅格结构的光学孔径面积略微变小,因此光学串扰得到了极大的抑制。光学串扰抑制的直接证据,在量子效率光谱上得到体现。图中三个黄色箭头指出了R、G、B通道的串扰抑制证据。蓝光通道和红光通道反应略微下降,但是通过新开发的颜色滤光片材料,绿光通道的量子效率得到了提升。利用Wafer Level Quantum Efficiency Spectrum技术可以直接证明光学串扰的抑制现象。对于不同的CIS图像芯片,可以通过量子效率光谱测试来比较它们在不同波长下的量子效率响应,进而分辨optical crosstalk是否得到抑制。上图展示了0.9um像素的量子效率光谱,其中虚线代表控制的0.9um像素(a),实线代表改进的0.9um像素(b)。由于栅格结构的光学孔径面积略微变小,因此光学串扰得到了极大的抑制。光学串扰抑制的直接证据,在量子效率光谱上得到体现。图中三个黄色箭头指出了R、G、B通道的串扰抑制证据。C. Color filter quality inspection(1) 什么是CIS 的Color filter?CIS的Color filter是一种用于CIS图像芯片的光学滤光片。它被用于调整图像传感器中各个像素的光谱响应,以便使得CIS图像芯片可以感测和分离不同颜色的光,并将其转换为数字信号。Color filter通常包括红、绿、蓝三种基本的色彩滤光片。而对于各种不同filter排列而成的color filter array (CFA),可以参考下面的资料。最常见的CFA就是Bayer filter的排列,也就是每个单元会有一个B、一个R、与两个G的filter排列。Color filter在CIS图像芯片中扮演着非常重要的角色,其质量直接影响着图像的色彩再现效果。为了确保Color filter的性能符合设计要求,需要进行精确的光谱分析和质量检测。透过率光谱可以评估不同Color filter的光学性能 量子效率光谱可以检测Color filter与光电二极管的匹配程度。只有通过严格的质量检测,才能保证CIS芯片输出优质的图像。图 Color filter 如何组合在“Pixel"传感器中。一个像素单位会是由Micro Lens + CFA + Photodiode等三个主要部件构成。Color filter的主要作用是将入射的白光分解成不同的色光,并且选择性地遮挡某些色光,从而实现对不同波长光的选择性感光。(2) 为什么Color filter的检测重要?在CIS图像芯片中,每个像素上都会有一个color filter,用来选择性地感光RGB三种颜色的光线,从而实现对彩色图像的捕捉和处理。如果color filter的性能不好,会影响像素的感光度和光谱响应,进而影响图像的品质和精度。因此,优化color filter的性能对于提高CIS图像芯片的品质至关重要。Color filter 的检测是十分重要的,因为color filter 的品质和稳定性会直接影响到CIS 图像芯片的色彩精确度和对比度,进而影响整个图像的品质和清晰度。如果color filter 存在缺陷或不均匀的情况,就会导致图像中某些颜色的偏移、失真、色彩不均等问题。因此,对color filter 进行严格的检测,可以帮助制造商确保其性能和品质符合设计要求,从而提高CIS 图像芯片的生产效率和产品的可靠性。(3) 如何利用QE光谱来检测CIS 的Color filter quality?CIS的Color filter通常是由一种称为“有机色料"(organic dyes or pigments)的物质制成,这些有机色料能够选择性地吸收特定波长的光,以产生所需的颜色滤波效果。这些有机色料通常是透过涂布技术将它们沉积在玻璃或硅基板上形成彩色滤光片。量子效率(QE)光谱可以测量CIS在不同波长下的感光度,从而确定Color filter的品质和性能。正常情况下,Color filter应该能够适当地分离不同波长的光,并且在光学过程中产生较小的串扰。因此,如果在特定波长下的量子效率比预期值低,可能是由于Color filter的品质或性能问题引起的。通过对量子效率 (QE)光谱的分析,可以确定Color filter的性能是否符合设计要求,并提前进行相应的调整和优化。TSMC利用Wafer Level Quantum Efficiency Spectrum晶片级量子效率光谱技术,对不同的绿色滤光片材料进行检测,以评估其对CIS图像芯片的感光能力和光学串扰的影响。如上图,TSMC的CIS工艺流程利用Wafer Level Quantum Efficiency Spectrum的光谱技术,针对不同的绿色滤光片材料进行检测,以评估其对CIS图像芯片的感光能力和光学串扰的影响。晶圆级量子效率光谱显示了三种不同Color filter材料(Green_1, Green_2和Green_3)的特性。透过比较这三种材料,可以发现:(1) 主要绿色峰值位置偏移至550nm(2) 绿光和蓝光通道的optical crosstalk现象显著降低(3) 绿光和红光通道的optical crosstalk现象显著增加。通过对量子效率(QE)光谱的分析,可以确定Color filter的性能是否符合设计要求,并提前进行相应的调整和优化。以确保滤光片材料的特性符合设计要求,并且保证图像的品质和精度,提高CIS图像芯片的可靠性和稳定性。D. Si 晶圆厚度控制(1) 什么是Si 晶圆厚度控制?当我们在制造BSI CIS图像芯片时,需要使用一种称为"减薄(thin down)"的工艺来将晶圆变得更薄。这减薄后的晶圆厚度会直接影响CIS芯片的感光度,因此晶圆的厚度对图像芯片的感光性能和质量都有很大的影响。为了确保图像芯片能够正常工作,我们需要使用"Si 晶圆厚度控制"工艺来精确地控制晶圆的厚度。这样可以确保我们减薄出来的晶圆厚度能够符合设计要求,同时也可以提高图像芯片的产品良率。BSI的流程图。采用BSI工艺的CIS图像芯片,会有一道重要的工艺“减薄"(Thin down), 也就是将晶圆的厚度减少到一定的程度。(2) Si 晶圆厚度控制工艺监控中的量子效率检测非常重要在制造CIS芯片时,Si 晶圆厚度控制工艺的控制对于芯片的感光度有着直接的影响。这种影响可以透过量子效率光谱来观察,确保减薄后的CIS芯片拥有相当的光电转换量子效率。减薄后的晶圆会有一个最佳的厚度值,可以确保CIS芯片拥有最佳的光电转换量子效率。使用450nm、530nm和600nm三种波长,可以测试红色、绿色和蓝色通道的量子效率。实验结果显示了不同减薄厚度的CIS在蓝光、绿光、红光通道的量子效率值的变化。减薄厚度的偏差会对CIS的感光度产生直接的影响,进而影响量子效率的值。因此,量子效率的检测对于Si 晶圆厚度控制工艺的监控至关重要,以确保制造的CIS芯片具有稳定和一致的质量。下图显示了在不同减薄厚度下CIS图像芯片在蓝、绿、红三个光通道的量子效率值变化。蓝光通道的量子效率值是利用450nm波长测量的,当减薄后的厚度比标准厚度多0.3um时,其量子效率值会由52%下降至49% 当减薄后的厚度比标准厚度少0.3um时,蓝光通道的量子效率只略微低于52%。红光通道的量子效率值是利用600nm波长测量的,发现红光通道的表现在不同厚度下与蓝光通道相反,当减薄后的厚度比标准厚度少0.3um时,红光通道的量子效率显著地由44%下降至41%。在较厚的条件(+0.3um)下,红光通道的量子效率并没有显著的变化。绿光通道的量子效率值是以530nm波长测量的,在三种厚度条件下(STD THK ± 0.3um),绿光通道的量子效率没有显著的变化。利用不同的Si晶圆厚度(THK)对CIS图像芯片的量子效率进行测试,测试波长分别为600nm、530nm和450nm,并且针对红色、绿色和蓝色通道的量子效率进行评估。结果显示,在绿光通道方面,Si晶圆厚度的变化在±0.3um范围内,530nm波段的量子效率并未有明显变化。但是,在红光通道方面,随着Si晶圆厚度的下降,量子效率会有显著的下降。而在蓝光通道450nm的情况下,量子效率会随着Si晶圆厚度的下降而有显著的下降。这些结果表明,Si晶圆厚度对于CIS图像芯片的量子效率有重要的影响,且不同通道的影响程度不同。因此,在制造CIS图像芯片时需要精确地控制Si晶圆厚度,以确保产品的质量和性能。